\$50 ELSEVIER

Contents lists available at ScienceDirect

## Microelectronic Engineering

journal homepage: www.elsevier.com/locate/mee

# The profile of temperature and voltage dependent series resistance and the interface states in (Ni/Au)/Al<sub>0.3</sub>Ga<sub>0.7</sub>N/AlN/GaN heterostructures

Z. Tekeli <sup>a,\*</sup>, Ş. Altındal <sup>a</sup>, M. Çakmak <sup>a</sup>, S. Özçelik <sup>a</sup>, E. Özbay <sup>b</sup>

- <sup>a</sup> Physics Department, Faculty of Arts and Sciences, Gazi University, Ankara 06500, Turkey

- b Nanotechnology Research Center, Department of Physics, Department of Electrical and Electronics Engineering, Bilkent University, Bilkent, Ankara 06800, Turkey

#### ARTICLE INFO

#### Article history: Received 19 March 2008 Received in revised form 28 July 2008 Accepted 24 August 2008 Available online 31 August 2008

Keywords: Al<sub>0.3</sub>Ga<sub>0.7</sub>N/AIN/GaN heterostructures Temperature dependence Series resistance Interface states Nitride passivation

#### ABSTRACT

The temperature dependence of capacitance–voltage (C-V) and the conductance–voltage (G/w-V) characteristics of (Ni/Au)/Al<sub>0.3</sub>Ga<sub>0.7</sub>N/AlN/GaN heterostructures were investigated by considering the effect of series resistance ( $R_s$ ) and interface states  $N_{ss}$  in a wide temperature range (79–395 K). Our experimental results show that both  $R_s$  and  $N_{ss}$  were found to be strongly functional with temperature and bias voltage. Therefore, they affect the (C-V) and (G/w-V) characteristics. The values of capacitance give two peaks at high temperatures, and a crossing at a certain bias voltage point ( $\sim$ 3.5 V). The first capacitance peaks are located in the forward bias region ( $\sim$ 0.1 V) at a low temperature. However, from 295 K the second capacitance peaks appear and then shift towards the reverse bias region that is located at  $\sim$ -4.5 V with increasing temperature. Such behavior, as demonstrated by these anomalous peaks, can be attributed to the thermal restructuring and reordering of the interface states. The capacitance ( $C_m$ ) and conductance (G/w-V) values that were measured under both reverse and forward bias were corrected for the effect of series resistance in order to obtain the real diode capacitance and conductance. The density of  $N_{ss}$ , depending on the temperature, was determined from the (C-V) and (G/w-V) data using the Hill–Coleman Method.

$\ensuremath{\text{@}}$  2008 Elsevier B.V. All rights reserved.

#### 1. Introduction

Owing to their large and direct band gap as well as favorable transport properties, GaN and related semiconductors have attracted intense interest from researchers in the last three decades. Moreover, III-V nitrides could be suitable for the emitters and detectors of green and shorter wavelengths, in turn making investments in this class of materials more than worthwhile [1-3]. Gallium nitride (GaN) and related compounds have been studied extensively for applications in short wavelength optical devices and high power/temperature devices, such as light emitting diodes (LEDs), laser diodes (LDs), metal oxide semiconductor field effect transistors (MOSFETs), and rectifiers. The performance of these devices especially depends on the formation of high quality ohmic and Schottky contacts [4-7]. The performance of metal-semiconductor (MS) Schottky diodes, metal-insulator-semiconductor (MIS) or metal-oxide-semiconductor (MOS) structures, solar cells, and high-electron-mobility transistor (HEMT) heterostructures depends on various factors, such as the interface preparation process, the metal to semiconductor barrier height (BH), device temperatures, insulator layer formation at the metal/semiconductor interface, interface states, and series resistance [8-13]. Thermally stable

Schottky contacts are required for the application of power amplifiers and optoelectronic devices operating at high temperatures. Therefore, the main scientific and technical problems of these devices are currently especially relevant to the decrease of series resistance, interface states, and the increase of the homogeneity of the barrier height at the metal/semiconductor interface. Recently, the temperature dependence of the electrical characteristics of MS and MIS structures has become an object of rather intense interest in the literature for more than four decades now [14–25]. However, complete descriptions of the effect of these parameters on the current–voltage (*I–V*) and *C–V* characteristics still remain a challenging problem. AlGaN/GaN heterostructures are seen as one of the most promising candidates for their potentially superior performance in high power and high frequency electronic devices [26,27].

The formation of Schottky contacts with high Schottky barrier heights (SBHs), low leakage current, and good thermal stability are the most important factors in enhancing the electrical performance of AlGaN/GaN heterostructures, especially regarding the power performances [28]. Ohmic and Schottky/rectifier contacts on GaN and AlGaN are widely studied, in which many results have been published thus far [29]. However, various preparation conditions and metallization systems, along with often contradictious results, have been reported. This might be because of the different layer quality (surface roughness, various defects, etc.) and surface

<sup>\*</sup> Corresponding author. Tel.: +90 3122021248; fax: +90 3122122279. E-mail address: zeki06us@yahoo.com (Z. Tekeli).

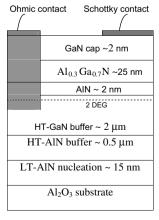

preparation (difficult wet etching) of the samples used. The most often applied metallization for ohmic contacts to GaN is Ti/Al, which needs to be annealed at a relatively high temperature. An Au cover layer is commonly used in order to prevent the oxidation of Ti/Al and Ni, or a Pt barrier layer is then inserted between Al and Au. On the other hand, Ni or Pt is used for the preparation of Schottky contacts because of their highest metal work function on GaN and AlGaN [30]. When a typical Schottky diode in ambient conditions is fabricated, there exists an insulating interfacial layer between the metal and semiconductor surface [31]. Commonly, the GaN surface that has been exposed to the air is contaminated with oxygen and carbon [32-34]. It is noteworthy that especially at low temperatures (LT) the GaN cap layer behaves like an insulator between the metals and semiconductor with extremely large sheet resistivity [35,36]. The purpose of the GaN cap layer is to prevent the reaction and inter-diffusion between the (Ni/Au) metals and semiconductor as well as to improve the respective retention properties. As seen in Fig. 1, the GaN cap and Al<sub>0.3</sub>Ga<sub>0.7</sub>N layers with a large lattice mismatch regarding the substrate, in turn form a mosaic structure of slightly misoriented sub-grains [37-41], which is characterized by the nucleation of slightly misoriented islands and the coalescence of these islands towards a smooth surface. The mosaic structure of the epilayers is determined by the size and angular distribution of the mosaic blocks. The vertical and lateral correlation lengths, heterogeneous strain, and degree of mosaicity as expressed by the tilt and twist angles are important parameters in characterizing the quality of the epitaxial films with a large lattice mismatch to the substrate [37,39,42].

In previous works, we examined the temperature dependence of the I–V characteristics formed ohmic and Schottky/rectifier contacts on this device [43] and the morphological properties as labeled sample A [44]. One of the very recent studies on the structural, morphological, and optical properties of this heterostructure was examined as a labeled sample B [45].

Now, the main aim of the present study investigates the temperature dependence of the forward and reverse bias C-V and G/W-V characteristics of (Ni/Au)/Al $_{0.3}$ Ga $_{0.7}$ N/AlN/GaN heterostructures by considering the  $R_{\rm s}$  and  $N_{\rm ss}$  effect. Therefore, in order to obtain a better understanding of the effects of  $R_{\rm s}$  and  $N_{\rm ss}$  on the C-V and (G/W-V) characteristics, we obtained forward and reverse bias C-V and (G/W-V) curves in a wide temperature range of 79–395 K at 1 MHz. In order to determine the values of  $R_{\rm s}$  and  $N_{\rm ss}$ , we applied the method developed by Nicollian and Goetzberger [13] and the Hill-Coleman method [46], respectively. The experimental results show that both  $R_{\rm s}$  and  $N_{\rm ss}$  are important parameters that influence the electrical characteristics of this device.

Fig. 1. Schematic diagram of the (Ni/Au)/Al<sub>0.3</sub>Ga<sub>0.7</sub>N/AlN/GaN heterostructures.

#### 2. Experiment

The Al<sub>0.3</sub>Ga<sub>0.7</sub>N/GaN heterostructure with a high temperature (HT)-AlN buffer layer (BL), as was investigated in the present study. was grown on a c-face sapphire (Al<sub>2</sub>O<sub>3</sub>) substrate by low-pressure metal-organic chemical vapor deposition (MOCVD). Hydrogen was used as the carrier gas and trimethylgallium (TMGa), trimethylaluminum (TMAI), and ammonia (NH3) were used as source compounds. Prior to the epitaxial growth, Al<sub>2</sub>O<sub>3</sub> substrate was annealed at 1100 °C for 10 min to remove all of the surface contamination. As shown in Fig. 1, a 15 nm-thick AlN nucleation layer was deposited on an Al<sub>2</sub>O<sub>3</sub> substrate at 840 °C. Then, the reactor temperature was ramped to 1150 °C and an HT-AlN BL was grown, followed by a two minute growth interruption in order to reach the growth conditions for GaN. GaN BL was grown at a reactor pressure of 200 mbar, growth temperature of 1070 °C, and growth rate of approx. 2 µm/h. Then, for a sample, a 2 nm-thick HT-AlN inter laver was grown at a temperature of 1085 °C and a pressure of 50 mbar. Finally, a 25 nm-thick AlGaN ternary layer and 2 nmthick GaN cap layer growth was carried out at a temperature of 1085 °C and a pressure of 50 mbar, respectively.

For the contacts, since the sapphire substrate is insulating, the ohmic and Schottky contacts were made on the top surface as 2 mm-diameter circular dots. Prior to ohmic contact formation. the samples were cleaned with acetone in an ultrasonic bath. Then, the sample was treated with boiling isopropyl alcohol for 5 minutes and rinsed in de-ionized (DI) water. After this cleaning, the samples were dipped in a solution of HCl/H<sub>2</sub>O (1:2) for 30 s in order to remove the surface oxides, and rinsed in DI water again for a prolonged period. For contact formation, Ti/Al/Ni/Au (200/2000/ 400/500 Å) metals were thermally evaporated on the sample. After the metallization step, the contacts were annealed at 850 °C for 30 s in N<sub>2</sub> ambient in order to form the ohmic contact. The formation of the ohmic contact was followed by Ni/Au (350/500 Å) evaporation as Schottky contacts. Prior to Schottky metal deposition, the same cleaning procedure for ohmic contacts was used for cleaning the sample surface.

The temperature dependence C-V and G/w-V measurements were performed at 1 MHz in the temperature range of 79–395 K by using an HP 4192 A LF impedance analyzer (5 Hz–13 MHz) and test signal of 40 mV<sub>rms</sub>. All of the measurements were carried out with a temperature controlled Janes vpf-475 cryostat, which enabled us to make measurements in the temperature range of 77–450 K, in which the sample temperature was always monitored by Lake Shore model 321 auto-tuning temperature controllers with sensitivity better than  $\pm$  0.1 K.

#### 3. Results and discussion

There are several methods for the calculation values of  $R_s$  between the semiconductor and interfacial insulator layer of Schottky diodes, MS and MIS structures. The theoretical expression of  $R_{\rm s}$  is still unclarified and is not clearly disclosed in the literature [13,47-49]. However, to extract the series resistance of these devices, a method developed by Nicollian and Goetzberger [13] is thought to be generally more useful than other methods. This method provides the determination of  $R_s$  in both reverse and forward bias regions. C-V-T and G/w-V-T characteristics of (Ni/Au)/ GaN/Al<sub>0.3</sub>Ga<sub>0.7</sub>N heterostructures were measured in the temperature range of 79-395 K. At sufficiently high frequencies ( $f \ge 500 \text{ kHz}$ ), the interface states cannot follow the ac signal, because at high frequencies the carrier life time  $\eta$  is larger than  $T = \frac{1}{2\pi f}$  [13]. Therefore, the real series resistance of the MIS devices can be subtracted from the measured capacitance ( $C_{ma}$ ) and conductance ( $G_{\text{ma}}$ ) and in the strong accumulation region at a high frequency (1 MHz) [13,16,50]. In addition to voltage dependence, the

temperature dependence of the series resistance can be obtained from the measurements of C-V-T and G/w-V-T curves. At a sufficiently high frequency, in order to determine  $R_{\rm s}$  the MS or MIS structures are biased into a strong accumulation. Then, admittance  $Y_{\rm ma}$  is given by [13]

$$Y_{ma} = G_{ma} + j\omega C_{ma} \tag{1}$$

Series resistance is the real part of the impedance and can be expressed as [13]

$$R_{s} = \frac{G_{ma}}{G_{ma}^{2} + \left(\omega C_{ma}\right)^{2}} \tag{2}$$

where  $C_{\rm ma}$  and  $G_{\rm ma}$  represent the measured capacitance and conductance in the strong accumulation region. The capacitance of the insulator layer  $C_{\rm ox}$  is obtained by substituting  $R_{\rm s}$  into the relation

$$C_{\text{ma}} = \frac{C_{\text{ox}}}{(1 + \omega^2 R_{\text{s}}^2 C_{\text{ox}}^2)}$$

(3)

From this relation,  $C_{ox}$  is obtained as

$$C_{\text{ox}} = C_{\text{ma}} \left[ 1 + \left( \frac{G_{\text{ma}}}{\omega C_{\text{ma}}} \right)^2 \right] = \frac{\varepsilon_i \varepsilon_o A}{d_{\text{ox}}}$$

(4)

where  $\varepsilon_{\rm i}\approx 10\varepsilon_0$  [51,52] and  $\varepsilon_0$  (=8.85  $\times$  10<sup>-14</sup> F/cm) are the permittivity of the interfacial insulator layer and free space, respectively, which was found to be 2.1  $\times$  10<sup>-8</sup> F. Thus, the corrected capacitance  $C_{\rm c}$ , and conductance  $G_{\rm c}$  values were obtained in the temperature region of 79–395 K at a high frequency of 1 MHz from the directly measured  $C_{\rm m}$  and  $G_{\rm m}$  according to

$$C_{c} = \frac{[G_{m}^{2} + (\omega C_{m})^{2}]C_{m}}{a^{2} + (\omega C_{ma})^{2}}$$

(5)

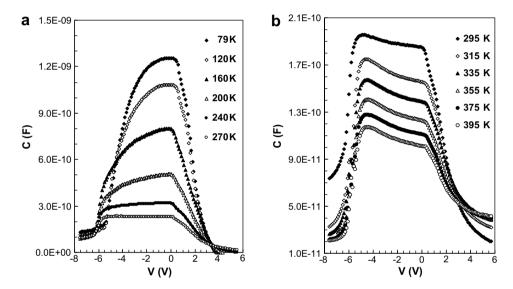

Fig. 2. The temperature dependent curves of the C-V characteristics for  $(Ni/Au)/Al_{0.3}Ga_{0.7}N/AlN/GaN$  heterostructures as measured at 1 MHz: (a) at low temperatures (from 79 to 270 K) and (b) at high temperatures (from 295 to 395 K).

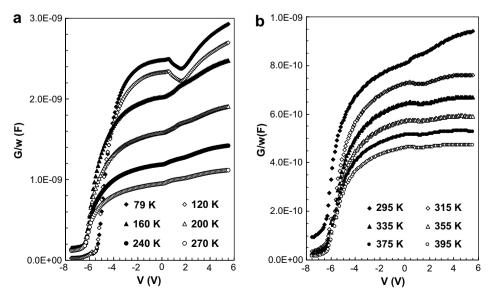

**Fig. 3.** The temperature dependent curves of the G/w-V characteristics for (Ni/Au)/Al<sub>0.3</sub>Ga<sub>0.7</sub>N/AlN/GaN heterostructures: (a) at low temperatures (from 79 to 270 K) and (b) at high temperatures (from 295 to 395 K).

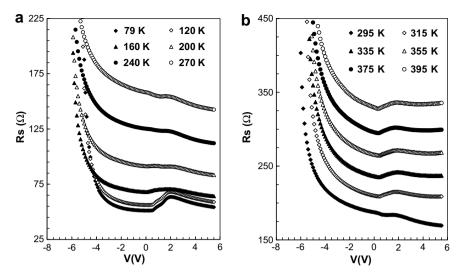

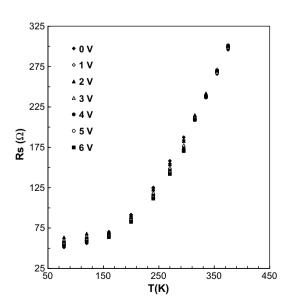

Fig. 4. The temperature dependent curves of the series resistance for  $(Ni/Au)/Al_{0.3}Ga_{0.7}N/AlN/GaN$  heterostructures measured at 1 MHz: (a) at low temperatures (from 79 to 295 K) and (b) at high temperatures (from 295 to 395 K).

and

$$G_{c} = \frac{[G_{m}^{2} + (\omega C_{m})^{2}] a}{a^{2} + (\omega C_{m})^{2}}$$

(6)

where  $a = G_{\rm m} - [G_{\rm m}^2 + (\omega C)^2]R_{\rm s}$ . The insulator layer thickness calculated from Eq. (4) was found to be 29.8 Å.

The measurement of the density of  $N_{\rm ss}$  is a useful guide for the quality of MS and MIS type structures. In order to determine the density of  $N_{\rm ss}$ , several methods have been suggested in the literature [46,53–56]. A fast and reliable way to determine the density of  $N_{\rm ss}$  is the Hill–Coleman method [46]. Therefore, in the present study the density of the interface state was obtained from the combination of various temperature C-V and G/w-V characteristics (Figs. 2 and 3).

According to the Hill-Coleman method, the density of the interface states can be expressed as

$$N_{ss} = \frac{2}{qA} \frac{(G_{ma}/\omega)_{max}}{((G_{ma}/\omega)_{max}C_{ox})^2 + (1 - C_{ma}/C_{ox})^2)}$$

(7)

where, A is the area of the rectifier contact,  $\omega$  is the angular frequency,  $C_{\rm m}$  and  $(G_{\rm m}/\omega)_{\rm max}$  are the measured capacitance and conductance that correspond to the peak values, respectively, and  $C_{\rm ox}$  is the capacitance of the insulator layer.

In general, the C-V and G/w-V characteristics of an MIS structure exhibit accumulation, depletion, and inversion regions. Fur-

**Table 1** The values of the various parameters for  $(Ni/Au)/Al_{0.3}Ga_{0.7}N/AlN/GaN$  heterostructures as obtained from the C-V and G/w-V characteristics in the temperature range of 79–395 K

| T(K) | $V_{\rm m}\left(V\right)$ | C (nF) | G/w (nF) | $R_{\rm s}\left(\Omega\right)$ | $N_{\rm ss}~({\rm eV}^{-1}~{\rm cm}^{-2})\times 10^{12}$ |

|------|---------------------------|--------|----------|--------------------------------|----------------------------------------------------------|

| 79   | 0.0                       | 1.26   | 2.48     | 51                             | 1.18                                                     |

| 120  | 0.1                       | 1.08   | 2.33     | 57                             | 1.03                                                     |

| 160  | 0.1                       | 0.79   | 2.02     | 68                             | 0.87                                                     |

| 200  | 0.1                       | 0.50   | 1.58     | 91                             | 0.66                                                     |

| 240  | 0.1                       | 0.32   | 1.19     | 125                            | 0.49                                                     |

| 270  | 0.1                       | 0.23   | 0.95     | 159                            | 0.38                                                     |

| 295  | 0.1                       | 0.18   | 0.81     | 187                            | 0.33                                                     |

| 315  | 0.2                       | 0.15   | 0.73     | 209                            | 0.29                                                     |

| 335  | 0.3                       | 0.14   | 0.65     | 235                            | 0.26                                                     |

| 355  | 0.3                       | 0.12   | 0.57     | 265                            | 0.23                                                     |

| 375  | 0.3                       | 0.11   | 0.51     | 295                            | 0.21                                                     |

| 395  | 0.3                       | 0.10   | 0.46     | 328                            | 0.18                                                     |

thermore, the behaviors of C-V and G/w-V characteristics are different in these regions. For example, while the values of  $R_s$  are effective at a sufficiently forward bias region, the values of  $N_{ss}$ are effective for the inversion and depletion regions. Therefore, the investigation of  $R_s$  and  $N_{ss}$  from a sufficiently low bias region to a high bias region is more important to clarify the behavior of C-V and G/w-V characteristics. Moreover, it is well known that the analysis of C-V and G/w-V characteristics of these devices, such as MS and MIS type Schottky diodes that are only at room temperature and for one bias voltage of C and G/w cannot provide us with detailed information about the temperature and bias voltage dependence of the conduction process or behavior of electrical parameters. Contrarily, in the wide temperature and bias voltage regions (both forward and reverse bias regions) of the C-V and G/ w-V measurements of these devices enable us to understand the different aspects of the conduction process or the temperature and bias voltage dependence behavior of electrical parameters. The temperature dependent C-V and G/w-V characteristics of

**Fig. 5.** The temperature dependent curves of the series resistance for  $(Ni/Au)/Al_{0.3}Ga_{0.7}N/AlN/GaN$  heterostructures for various forward biases at 1 MHz.

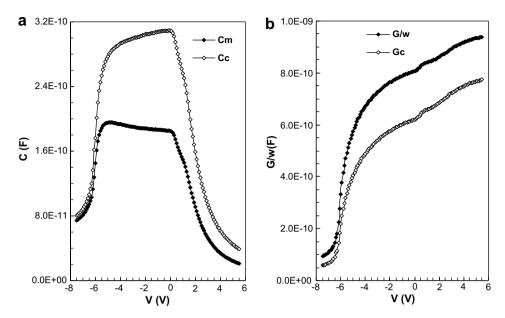

**Fig. 6.** The voltage dependent curves of the corrected (a)  $C_c$ –V and (b)  $G_c/w$ –V characteristics for (Ni/Au)/Al<sub>0.3</sub>Ga<sub>0.7</sub>N/AlN/GaN heterostructures at room temperature measured at 1 MHz.

(Ni/Au)/Al<sub>0.3</sub>Ga<sub>0.7</sub>N/AlN/GaN heterostructures that were measured at 1 MHz are shown in Figs. 2 and 3. As seen in Fig. 2a and b, the first peak's position is located at a forward bias of capacitance and shifts towards the reverse bias region with increasing temperature. The values of the various parameters for (Ni/Au)/Al<sub>0.3</sub>Ga<sub>0.7</sub>N/AlN/GaN heterostructures as determined from *C–V* and *G/w–V* characteristics in the temperature range of 79–395 K are shown in Table 1.

The values of  $R_s$  and  $N_{ss}$ , as shown in Table 1, correspond to the peak value of capacitance at a forward bias for each temperature and are calculated according to Eqs. (2) and (3), respectively, and the voltage dependence of the  $R_s$  profile at each temperature is shown in Fig. 4a and b. Moreover, the temperature dependence of  $R_s$  for a different forward bias at a high frequency is shown in Fig. 5. It is clearly seen in Fig. 5 that  $R_s$  is nearly independent of bias voltage at low temperatures ( $T \le 200$  K). These very significant values demanded special attention to be given to the effects of the series resistance in the application of the admittance-based measured methods (C-V and G/w-V).

As can be seen in Fig. 5, the  $R_{\rm s}$  values are nearly independent of the voltage at low temperature and at the high forward bias region. As seen in Fig. 4a and b, it is clear that the series resistance is strong with the voltage and temperature in the temperature range of 79–395 K and increases with increasing temperature. This change in  $R_{\rm s}$  becomes rather important in the high reverse bias. It is also clear that in the high forward bias the values of  $R_{\rm s}$  are nearly independent of the temperature. Such temperature dependence of  $R_{\rm s}$  (Fig. 5) is an obvious disagreement with the reported negative temperature coefficient of  $R_{\rm s}$  of Schottky diode, MS, MIS, or MOS structure. This variation of  $R_{\rm s}$  with the temperature can be expected for semiconductors in the temperature region where there is no freezing behavior of the carriers. We believe that the trap charges have sufficient energy to escape from the traps that are located between the metal and semiconductor interface in the  $Al_{0.3}Ga_{0.7}N$  band gap.

As seen in Fig. 2 a, due to the series resistance, C-V plots give a peak for each temperature. Similar results have been reported in the literature [24,57–60]. To obtain the real diode capacitance ( $C_c$ ) and conductance ( $C_c/w$ ), the high frequency capacitance as measured under forward and reverse bias was corrected for the effect of series resistance using Eqs. (5) and (6), respectively. As can

be seen in Fig. 6 a, a correction was made on the C-V plot for the effect of series resistance in the accumulation and depletion regions where the values of the corrected capacitance increase with increasing voltage, especially in the depletion regions. On the other hand, the plot of the corrected conductance decreases with increasing voltage except for very low negative biases ( $V \le 6$  V).

#### 4. Conclusion

The forward and reverse bias capacitance-voltage-temperature (C-V-T) and conductance-voltage-temperature (G/w-V-T) characteristics of (Ni/Au)/GaN/Al<sub>0.3</sub>Ga<sub>0.7</sub>N heterostructures were measured in the temperature range of 79-395 K. R<sub>s</sub> and the density of the  $N_{ss}$  effects of the sample on the C-V and G/w-V characteristics were investigated. It was found that capacitance and conductance were quite sensitive to temperature, especially at a relatively high temperature, in which the values  $N_{ss}$  and  $R_s$  decrease with increasing temperature. This behavior was attributed to the thermal restructuring and reordering of the interface. The crossing of the C-V plots and the behavior of  $R_s$  appear to be abnormal compared to the conventional behavior of a Schottky diode, an MIS, or MOS structure. Such behavior of C-V curves and R<sub>s</sub> with regard to the temperature can be expected for semiconductors in the temperature region where there is no freezing behavior of the carriers. C-V and G/w-V characteristics confirm that N<sub>ss</sub> and the thickness of the insulator layer  $(\delta)$  are important parameters that strongly influence the electric parameters in the MIS structure.

### References

- H. Morkoc, S. Strite, G.B. Gao, M.E. Lin, B. Sverdlov, M. Burns, J. Appl. Phys. Rev. 76 (1994) 1363.

- [2] S.N. Mohammad, H. Morkoc, Prog. Quantum Electron. 20 (1996) 361.

- [3] S.N. Mohammad, H. Morkoc, Science 267 (1995) 51.

- [4] L.C. Chen, C.Y. Hsu, W.H. Lan, S.Y. Teng, Solid State Electron. 47 (2003) 1843.

- [5] R. Werner, M. Reinhardt, M. Emmerling, A. Forchel, V. Harle, A. Bazhenov, Physica E 7 (2000) 915.

- [6] D. Mistele, Mater. Sci. Eng. B 93 (2002) 107.

- [7] S. Pearton, Mater. Sci. Eng. B 82 (2001) 227.

- [8] T. Hashizume, S. Ootomo, S. Oyama, M. Konishi, H. Hasegawa, J. Vac. Sci. Technol. B 19 (2001) 1675.

- [9] S.M. Sze, Physics of Semiconductor Devices, second ed., Wiley, New York, 1981.

- [10] E.H. Rhoderick, R.H. Williams, Metal-Semiconductor Contacts, second ed., Clarendon Press, Oxford, 1988.

- [11] C.R. Crowell, S.M. Sze, J. Appl. Phys. 36 (1965) 3212.

- [12] H.C. Card, E.H. Rhoderick, J. Phys. D: Appl. Phys. 4 (1971) 1589.

- [13] E.H. Nicollian, J.R. Brews, Bell syst. Technol. J. 46 (1967) 1055.

- [14] S. Zeyrek, Ş. Altındal, H. Yüzer, M.M. Bülbül, Appl. Surf. Sci. 252 (2006) 2999.

- [15] Ş. Altındal, S. Karadeniz, N. Tuğluoğlu, A. Tataroğlu, Solid State Electron. 47 (2003) 1847.

- [16] A. Tataroğlu, Ş. Altındal, M.M. Bülbül, Microelectron. Eng. 81 (2005) 140.

- [17] P. Chattopadhyay, B. Raychaudhuri, Solid State Electron. 35 (1993) 605.

- [18] İ. Dökme, Ş. Altındal, Semicond. Sci. Technol. 21 (2006) 1053.

- [19] S. Chand, J. Kumar, Semicond. Sci. Technol. 11 (1996) 1203.

- [20] S. Chand, J. Kumar, Appl. Phys. A 65 (1997) 497.

- [21] Ş. Karataş, Ş. Altındal, A. Türüt, A. Özmen, Appl. Surf. Sci. 217 (2003) 250.

- [22] S. Zhu, R.L. Van Meirhaeghe, C. Detavernier, G.P. Ru, B.Z. Li, F. Cardon, Solid State Commun. 112 (1999) 611.

- [23] J.H. Werner, H.H. Güttler, J. Appl. Phys. 69 (1991) 1522.

- [24] S. Huang, S. Banerjee, R.T. Tung, S. Oda, J. Appl. Phys. 93 (2003) 576.

- [25] S. Huang, S. Banerjee, R.T. Tung, S. Oda, J. Appl. Phys. 94 (2003) 7261.

- [26] V. Kumar, W. Lu, F.A. Khan, R. Schwindt, A. Kuliev, G. Simin, J. Yang, M. Asif Khan, I. Adesida, Electron. Lett. 38 (2002) 252.

- [27] O. Ambacher et al., J. Appl. Phys. 87 (2000) 334.

- [28] C.M. Jeon, J.-L. Lee, J. Appl. Phys. 95 (2004) 698.

- [29] S.J. Pearton et al., J. Appl. Phys. 86 (1999) 1.

- [30] A.S. Schmitz et al., J. Electron. Mater. 27 (1998) 255.

- [31] H. Rohdin, N. Moll, A.M. Bratkovsky, C.Y. Su, Phys. Rev. B 59 (1999) 13102.

- [32] V.M. Bermudez, D.D. Koleske, A.E. Wickenden, Appl. Surf. Sci. 126 (1998) 69.

- [33] S.W. King, J.R. Barnak, M.D. Bremser, K.M. Tracy, C. Ronning, R.F. Davis, R.J. Nemanich, J. Appl. Phys. 84 (1998) 5248.

- [34] I. Shalish, Y. Shapira, L. Burnstein, J. Salzman, J. Appl. Phys. 89 (2001) 390.

- [35] M.L. Lee, J.K. Sheu, Y.K. Su, S.J. Chang, W.C. Lai, G.C. Chi, IEEE Electron. Device Lett. 25 (2004) 593.

- [36] E.J. Miller, X.Z. Dang, H.H. Wieder, P.M. Asbeck, E.T. Yu, G.J. Sullivan, J.M. Redwing, J. Appl. Phys. 87 (2000) 8070.

- [37] T. Metzger, R. Höppler, E. Born, O. Ambacher, M. Stutzmann, R. Stömmer, M. Schuster, H. Göbel, S. Christiansen, M. Albrecht, H.P. Strunk, Philos. Mag. A 77 (1998) 013.

- [38] B. Heying, X.H. Wu, S. Keller, Y. Li, D. Kapolnek, B.P. Keller, S.P. DenBaars, J.S. Speck, Appl. Phys. Lett. 68 (1995) 643.

- [39] M.E. Vickers, M.J. Kappers, R. Datta, C. McAleese, T.M. Smeeton, F.D.G. Rayment, C.J. Humphreys, J. Phys. D: Appl. Phys. 38 (2005) A99.

- [40] Nils G. Weimann, Lester F. Eastman, J. Appl. Phys. 83 (1998) 3656.

- [41] V. Holy, J. Kubena, E. Abramof, K. Lischka, A. Pesek, E. Koppensteiner, J. Appl. Phys. 74 (1993) 1736.

- [42] V. Srikant, J.S. Speck, D.R. Clarke, J. Appl. Phys. 82 (1997) 4286.

- [43] Z. Tekeli, Ş. Altındal, M. Çakmak, S. Özçelik, D. Çalışkan, E. Özbay, J. Appl. Phys. 102 (2007) 054510.

- [44] S. Çörekçi, D. Usanmaz, Z. Tekeli, M. Çakmak, S. Özçelik, E. Özbay, J. Nanosci. Nanotechnol. 8 (2008) 640.

- [45] S. Çörekçi, M.K. Öztürk, B. Akaoğlu, M. Çakmak, S. Özçelik, E. Özbay, J. Appl. Phys. 101 (2007) 123502.

- [46] W.A. Hill, C.C. Coleman, Solid State Electron. 23 (1980) 987.

- [47] H. Norde, J. Appl. Phys. 50 (1979) 5052.

- [48] K. Sato, Y. Yasamura, J. Appl. Phys. 58 (1985) 3656.

- [49] S.K. Cheung, N.W. Cheung, Appl. Phys. Lett. 49 (1986) 85.

- [50] K.K. Hung, Y.C. Cheng, J. Appl. Phys. 62 (1987) 4204.

- [51] S. Imanaga, H. Kawai, J. Appl. Phys. 82 (1997) 5843.

- [52] D.J.H. Lambert, D.E. Lin, R.D. Dupuis, Solid State Electron. 44 (2000) 253.

- [53] R. Castange, A. Vapaile, Surf. Sci. 28 (1971) 157.

- [54] U. Kelberlau, R. Kasing, Solid State Electron. 24 (1981) 873.

- [55] M. Kuhn, Solid State Electron. 13 (1970) 873.

- [56] S. Kar, S. Varma, J. Appl. Phys. 58 (1985) 4259.

- [56] S. Kar, S. Varma, J. Appl. Pnys. 58 (1985) 4258 [57] Ş. Karataş, A. Türüt, Vacuum 74 (2004) 45.

- [58] K.S. K Kwa, S. Chattopadhyay, N.D. Jankovic, H.S. Olsen, L.S. Driscoll, A.G. O'Neill, Semicond. Sci. Technol. 18 (2003) 82.

- [59] P. Cova, A. Singh, R.A. Masut, J. Appl. Phys. 82 (1997) 5217.

- [60] N. Konofaos, E.K. Evangelou, Semicond. Sci. Technol. 18 (2003) 56.