## Zinc-oxide charge trapping memory cell with ultra-thin chromium-oxide trapping layer

Nazek El-Atab, Ayman Rizk, Ali K. Okyay, and Ammar Nayfeh

Citation: AIP Advances 3, 112116 (2013); doi: 10.1063/1.4832237

View online: http://dx.doi.org/10.1063/1.4832237

View Table of Contents: http://scitation.aip.org/content/aip/journal/adva/3/11?ver=pdfcov

Published by the AIP Publishing

## Articles you may be interested in

Enhanced memory effect via quantum confinement in 16nm InN nanoparticles embedded in ZnO charge trapping layer

Appl. Phys. Lett. 104, 253106 (2014); 10.1063/1.4885397

Low power zinc-oxide based charge trapping memory with embedded silicon nanoparticles via poole-frenkel hole emission

Appl. Phys. Lett. 104, 013112 (2014); 10.1063/1.4861590

Diode behavior in ultra-thin low temperature ALD grown zinc-oxide on silicon

AIP Advances 3, 102119 (2013); 10.1063/1.4826583

Tuning of undoped ZnO thin film via plasma enhanced atomic layer deposition and its application for an inverted polymer solar cell

AIP Advances 3, 102114 (2013); 10.1063/1.4825230

Long-term stabilization of sprayed zinc oxide thin film transistors by hexafluoropropylene oxide self assembled monolayers

J. Appl. Phys. 114, 094512 (2013); 10.1063/1.4820458

Journal of Applied Physics is pleased to announce André Anders as its new Editor-in-Chief

## Zinc-oxide charge trapping memory cell with ultra-thin chromium-oxide trapping layer

Nazek El-Atab, <sup>1</sup> Ayman Rizk, <sup>1</sup> Ali K. Okyay, <sup>2,3</sup> and Ammar Nayfeh <sup>1</sup> Institute Center for Microsystems – iMicro, Department of Electrical Engineering and Computer Science (EECS), Masdar Institute of Science and Technology Abu Dhabi, United Arab Emirates

<sup>2</sup>Department of Electrical and Electronics Engineering, Bilkent University, 06800 Ankara, Turkey

<sup>3</sup>UNAM-National Nanotechnology Research Center and Institute of Materials Science and Nanotechnology, Bilkent University, 06800 Ankara, Turkey

(Received 11 October 2013; accepted 6 November 2013; published online 13 November 2013)

A functional zinc-oxide based SONOS memory cell with ultra-thin chromium oxide trapping layer was fabricated. A 5 nm  $CrO_2$  layer is deposited between Atomic Layer Deposition (ALD) steps. A threshold voltage ( $V_t$ ) shift of 2.6V was achieved with a 10V programming voltage. Also for a 2V  $V_t$  shift, the memory with  $CrO_2$  layer has a low programming voltage of 7.2V. Moreover, the deep trapping levels in  $CrO_2$  layer allows for additional scaling of the tunnel oxide due to an increase in the retention time. In addition, the structure was simulated using Physics Based TCAD. The results of the simulation fit very well with the experimental results providing an understanding of the charge trapping and tunneling physics. © 2013 Author(s). All article content, except where otherwise noted, is licensed under a Creative Commons Attribution 3.0 Unported License. [http://dx.doi.org/10.1063/1.4832237]

Nanotechnology has emerged as a vital enabler to allow memory devices to support future super hand-held computing devices.<sup>1-4</sup> In recent years, ZnO has been considered as a promising candidate to be used in flexible and/or transparent nano-devices due to its wide bandgap, good transparency, and low light sensitivity.<sup>4-7</sup> Earlier we validated a functional ZnO charge trapping memory grown by single step atomic layer deposition.<sup>4</sup> In this work, a ZnO based charge trapping memory cell is fabricated with a CrO<sub>2</sub> nanolayer sandwiched between the ALD deposited Al<sub>2</sub>O<sub>3</sub> tunnel and blocking oxides. In addition, the structure is simulated using TCAD which allowed the exploration of the CrO<sub>2</sub> charge trapping and tunneling models.

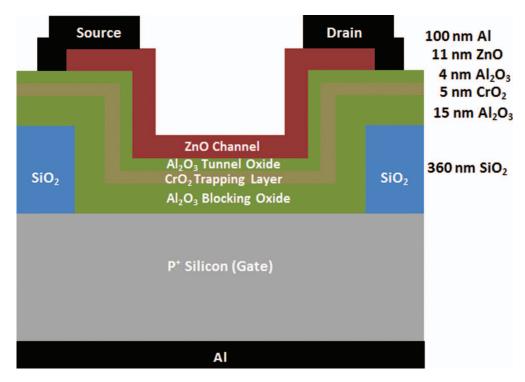

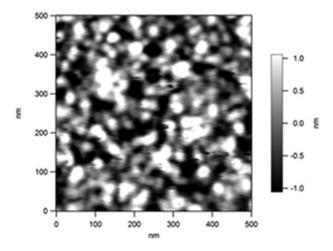

The bottom-gate memory devices are fabricated as follows: first a 15-nm-thick  $Al_2O_3$  blocking oxide layer is first ALD deposited followed by a sputtering of a 5-nm-thick  $CrO_2$  as the charge trapping layer, then a 4-nm-thick ALD deposited  $Al_2O_3$  tunneling oxide and finally an 11-nm-thick ALD deposited ZrO channel. A solution of 2:98  $H_2SO_4$ : $H_2O$  is used for 2 sec to etch the channel. A highly doped (10-18 milliohm-cm) p-type (111) silicon substrate is used as a back-gate electrode. The source and drain contacts were created by depositing 100 nm Al by thermal evaporation followed by lift off. Using Plasma Enhanced Chemical Vapor Deposition (PECVD), a 360-nm-thick  $SiO_2$  layer is deposited for device isolation. Finally, Rapid Thermal Annealing (RTA) in forming gas  $(H_2:N_2 5:95)$  for 10 min at  $400\,^{\circ}C$  was performed on the samples. Fig. 1 shows a cross section of the final device structure with the  $CrO_2$  nanolayer. Fig. 2 shows the atomic force microcopy (AFM) image of the  $CrO_2$  layer grown on top of the  $Al_2O_3$  layer. The RMS is 1-nm which highlights the continuity of the nanolayer.

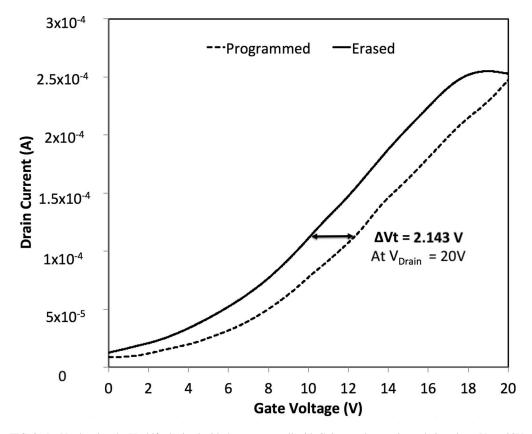

In order to study the effect of the  $CrO_2$  nanolayer, the threshold voltage is quantified before and after programing. The memory cell is programmed (writing a '1') by applying a constant voltage (+8V) for 15 sec on the gate while grounding the drain and source. In order to erase the memory cell by removing the charge trapped in the  $CrO_2$  layer, (writing a '0'), -8V is applied for 15 sec.

© Author(s) 2013

FIG. 1. Schematic cross-section of the fabricated memory cell with embedded CrO<sub>2</sub> nanolayer.

FIG. 2. AFM scan of the  $CrO_2$  deposited on the  $Al_2O_{3;}$  RMS =  $\sim 1$ nm.

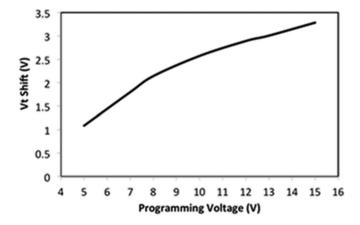

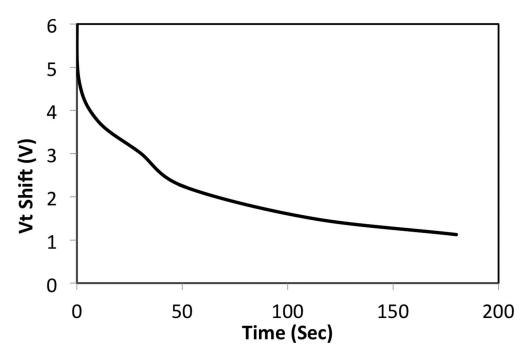

Fig. 3 shows the  $I_d$ -V $_g$  curve for both programming and erase states, and the structure with the  $CrO_2$  layer shows a  $V_t$  shift of 2.143V. Fig. 4 plots the threshold voltage shift vs. programming voltage. Compared to the ZnO charge trapping memory, 4 where we used a ZnO charge trapping layer; for a 2V  $V_t$  shift the  $CrO_2$  nanolayer layer provides a  $\sim$ 2.5V reduction in programming voltage. Fig. 5 plots  $V_t$  shift as a function of time. The figure shows a long retention time with the addition of the  $CrO_2$  layer. This is due to the extra states available and the larger barrier achieved between the charge trapping layer and the tunneling oxide. As a result, the tunnel oxide thickness can be scaled without sacrificing on retention.

Physics Based TCAD simulations using Synopsys<sup>TM</sup> TCAD tools are also studied. Because the experimental results showed a good charge trapping effect of the CrO<sub>2</sub> ultrathin layer with long retention time, and because there is no quantum well created by the CrO<sub>2</sub> layer due to its lower

FIG. 3.  $I_d$ – $V_g$  showing the  $V_t$  shift obtained with the memory cell with  $CrO_2$  nanolayer using a drain voltage  $V_d = 20V$ .

FIG. 4. Measured  $V_t$  shift vs. programming voltage.

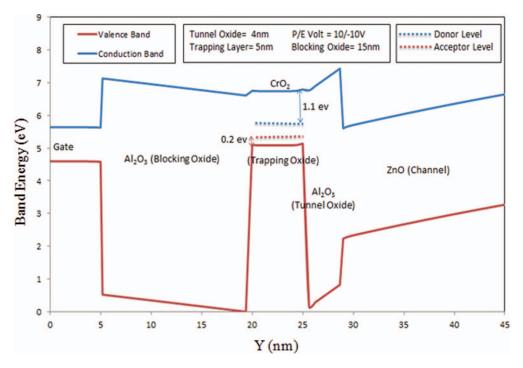

electron affinity than the adjacent oxides electron affinities, which means that the electrons must be trapped within the trapping states available in ZnO only; thus we modeled the CrO<sub>2</sub> nanolayer such that the charge trapping levels are deep with high densities. To the best of our knowledge, there are still no published studies on the CrO<sub>2</sub> charge trapping and tunneling properties, but using TCAD simulations we were able to get an approximate model of the CrO<sub>2</sub> trapping and tunneling characteristics such as trapping levels, trapping densities, and electron and hole effective masses. In fact, a wide combination of different trapping levels with different trapping densities, and electron and hole CrO<sub>2</sub> effective tunnel masses were tested using TCAD simulations. The final structure that gave similar results to the experimental ones has the following parameters: a donor level in CrO<sub>2</sub> at

FIG. 5. Measured V<sub>t</sub> shift vs time for the memory device with CrO<sub>2</sub> nanolayer.

FIG. 6. Energy band diagram of the memory cell with  $CrO_2$  nanolayer.

$1.1~{\rm eV}$  from the conduction band with a density of  $10^{21}~{\rm cm}^{-3}$ , an acceptor level in  ${\rm CrO_2}$  at  $0.2~{\rm eV}$  from the valence band with a density of  $10^{21}~{\rm cm}^{-3}$ , and electron and hole effective masses of  $0.29{\rm m0}$ . The energy band diagram of the simulated structure at zero applied voltage is depicted in Fig. 6. The tunneling models that were used in TCAD are: Fowler-Nordheim, trap assisted tunneling (TAT), and direct tunneling. These models are included to allow charges to tunnel across the tunnel oxide and charge or discharge the charge trapping ZnO layer when programming or erasing the memory cell.

TABLE I. Material properties for ZnO, Al<sub>2</sub>O<sub>3</sub>, and CrO<sub>2</sub>.

|                       | $Al_2O_3$ | ZnO       | CrO <sub>2</sub> |

|-----------------------|-----------|-----------|------------------|

| Energy bandgap        | 6.65 eV   | 3.37 eV   | 1.7 eV           |

| Relative permittivity | 9.5       | 8.75      | 5                |

| Electron affinity     | 2.58 eV   | 4.5 eV    | 2.41 eV          |

| Electron tunnel mass  | $0.43m_0$ | $0.24m_0$ | $0.29m_0$        |

| Hole tunnel mass      | $0.5m_0$  | $0.59m_0$ | $0.29m_0$        |

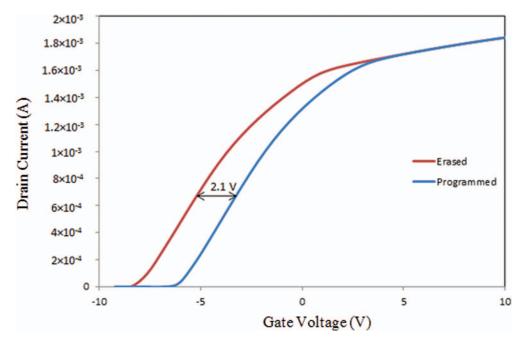

FIG. 7. Computed  $I_{drain} - V_{gate}$  for both program and erase states with P/E voltage of 8V/-8V.

Also, to ensure that the ZnO substrate is n-type due to crystallographic defects such as interstitial zinc and oxygen vacancies; <sup>7</sup> energy states were included in the ZnO layer of the TCAD simulated model. The material properties of ZnO, <sup>8</sup> Al<sub>2</sub>O<sub>3</sub>, <sup>9</sup> and CrO2<sup>10–12</sup> that were included in the simulations are listed in Table I. The I<sub>drain</sub> - V<sub>gate</sub> curves of the memory cell with an applied program/erase (P/E) voltage of 8V/–8V are shown in Fig. 7. The obtained V<sub>t</sub> shift of 2.1V is consistent with the V<sub>t</sub> shift obtained experimentally proving the accuracy of the proposed CrO<sub>2</sub> trapping and tunneling properties: electron and hole effective masses, charge trapping levels and their densities.

In summary, a ZnO charge trapping memory cell is fabricated with a  $CrO_2$  charge trapping layer. Experimental results combined with TCAD simulations provide an understanding of the charge trapping mechanisms. The memory achieved a 2.6V  $V_t$  shift, a reduced programming voltage, and a long retention time. The results show that use of ultra-thin nanolayers can reduce the required programming voltage for future nanomemory devices which is promising for future low cost electronic devices.

## **ACKNOWLEDGMENTS**

We gratefully acknowledge financial support for this work provided by the Masdar Institute of Science and Technology and the Advanced Technology Investment Company (ATIC).

<sup>&</sup>lt;sup>1</sup>R. Ohba, N. Sugiyama, K. Uchida, J. Koga, and A. Toriumi, "Non-volatile Si quantum memory with self-aligned doubly-stacked dots," IEEE Trans. Elec. Dev. 49, 1392 (2002).

<sup>&</sup>lt;sup>2</sup> J. De Blauwe, "Nanocrystal Nonvolatile Memory Devices," IEEE Transactions on Nanotechnology 1, 72 (2002).

<sup>&</sup>lt;sup>3</sup> C. gyu Hwang, "Nanotechnology enables a new memory growth model," Proceedings of the IEEE **91**, 1765 (2003).

- <sup>4</sup>F. B. Oruc, F. Cimen, A. Rizk, M. Ghaffari, A. Nayfeh, and A. K. Okyay, "Thin Film ZnO Charge-Trapping Memory Cell Grown in a Single ALD Step," IEEE Elec. Dev. Lett. **33**, 1714 (2012).

- <sup>5</sup>R. L. Hoffman, B. J. Norris, and J. F. Wager, "ZnO-based transparent thin-film transistors," Appl. Phys. Lett. **82**, 733 (2003).

- <sup>6</sup> A. Lu, J. Sun, J. Jiang, and Q. Wan, "Low-voltage transparent electric-double-layer ZnO-based thin-film transistors for portable transparent electronics," Appl. Phys. Lett. 96, 043114 (2010).

- <sup>7</sup>N. El-Atab, S. Alqatari, F. B. Oruc, T. Souier, M. Chiesa, A. K. Okyay, and A. Nayfeh, "Diode Behavior in Ultra-Thin Low Temperature ALD Grown Zinc-Oxide on Silicon," AIP Advances 3, 102119 (2013).

- <sup>8</sup> M. L. Huang, Y. C. Chang, C. H. Chang, T. D. Lin, J. Kwo, T. B. Wu, and M. Hong, "Energy-band parameters of atomic-layer-deposition-Al2O3/InGaAs hetero-structures," Appl. Phys. Lett. 89, 012903 (2006).

- <sup>9</sup> J. Bu and M. H. White, "Design considerations in scaled SONOS nonvolatile memory devices," Solid-State Electronics **45**, 113 (2001).

- <sup>10</sup> J. M. D. Coey, A. E. Berkowitz, Ll. Balcells, and F. F. Putris, "Magnetoresistance of Chromium Dioxide Powder Compacts," Physical Review Letters 80, 3815 (1998).

- <sup>11</sup> C. A. Ventrice Jr, D. R. Borst, H. Geisler, J. van Ek, Y. B. Losovyj, P. S. Robbert, U. Diebold, J. A. Rodriguez, G. X. Miao, and A. Gupta, "Are the surfaces of CrO<sub>2</sub> metallic?," J. Phys.: Condens. Matter. 19, 315207 (2007).

- $^{12}$ G. L. Gutseva and P. Jena, "Electronic structure of chromium oxides,  $CrO_n^-$  and  $CrO_n$ ,, (n = 1 5) from photoelectron spectroscopy and density functional theory calculations," J. Chem. Phys. 115, 7935 (2001).