This article was downloaded by: [Bilkent University]

On: 26 February 2013, At: 06:02

Publisher: Taylor & Francis

Informa Ltd Registered in England and Wales Registered Number: 1072954 Registered office: Mortimer House, 37-41 Mortimer Street,

London W1T 3JH, UK

# International Journal of **Flectronics**

Publication details, including instructions for authors and subscription information: http://www.tandfonline.com/loi/tetn20

# An efficient program for analysis of interconnect circuits

MUSTAFA SUNGUR, A. SUAT EKINCI & ABDULLAH ATALAR Version of record first published: 10 Nov 2010.

To cite this article: MUSTAFA SUNGUR, A. SUAT EKINCI & ABDULLAH ATALAR (1997): An efficient program for analysis of interconnect circuits, International Journal of Electronics, 82:6, 641-654

To link to this article: http://dx.doi.org/10.1080/002072197135797

#### PLEASE SCROLL DOWN FOR ARTICLE

Full terms and conditions of use: http://www.tandfonline.com/page/ terms-and-conditions

This article may be used for research, teaching, and private study purposes. Any substantial or systematic reproduction, redistribution, reselling, loan, sub-licensing, systematic supply, or distribution in any form to anyone is expressly forbidden.

The publisher does not give any warranty express or implied or make any representation that the contents will be complete or accurate or up to date. The accuracy of any instructions, formulae, and drug doses should be independently verified with primary sources. The publisher shall not be liable for any loss, actions, claims, proceedings, demand, or costs or damages whatsoever or howsoever caused arising directly or indirectly in connection with or arising out of the use of this material.

# An efficient program for analysis of interconnect circuits

# MUSTAFA SUNGUR†, A. SUAT EKINCI† and ABDULLAH ATALAR†

A circuit simulation program using generalized asymptotic waveform evaluation techniques is introduced. The program analyses circuits with lumped and distributed components. It computes the moments at a few frequency points, and extracts the coefficients of an approximating rational by matching the moments simultaneously. The accuracy of the results and the execution times are compared with conventional simulators using several examples, indicating that our simulator provides a speed improvement without a significant loss of accuracy.

#### 1. Introduction

Accurate simulation of VLSI circuits for the large circuit sizes of today is difficult. Shrinking device sizes and increasing operating speeds require faster circuit simulation programs which do not trade execution time for accuracy. Spice-like programs with high accuracy are widely used for intensive verification and design of VLSI circuits, but for reducing execution times, new circuit solving algorithms are needed. While Spice-like simulators predict the behaviour of the circuit at a large number of discrete points both in frequency and time domain analysis, most of the new simulators employ faster algorithms to solve the circuit matrix at a lower number of points.

The asymptotic waveform evaluation (AWE) technique (Pillage and Rohrer 1990) is used in some new simulators in order to reduce the execution time of the simulation. Instead of solving the circuit at many discretized points, AWE seeks to capture the behaviour by approximating the dominant poles of the circuit with a lower order model. The reduced order model is matched to the moments of the linear circuit, which are obtained from the Taylor series expansion of the circuit response around s = 0. Since the information carried by the moments is accurate in the low frequency region, the AWE technique will be efficient in extracting the low frequency poles of the circuit. At relatively higher frequencies the AWE technique becomes inefficient and several methods are proposed to improve AWE's accuracy. AWE is extended to handle distributed elements (Tang and Nakhla 1992, Bracken et al. 1992) in order to analyse circuits that cannot be modelled by only lumped components. Also, Laurent series expansion ( $s = \infty$ ) is added to improve the accuracy of transient analysis in the vicinity of t = 0 (Huang et al. 1990). Stability of approximations is improved by manipulating the moment matching techniques (Anastakis et al. 1993). A complex frequency hopping technique is introduced in order to find all the dominant poles of the circuit in a frequency range of interest (Chiprout and Nakhla 1995). The PVL algorithm, Padé Approximation via the Lanczos Process is introduced to provide high numerical stability of Padé approximants (Feldmann and Freund 1995).

Received 5 September 1996; accepted 4 November 1996.

<sup>†</sup>Department of Electrical Engineering, Bilkent University, 06533, Ankara, Turkey.

Recently, a multi-point Padé approximation was proposed (Çelik *et al.* 1995) for analysis of interconnect networks with transmission lines, not only in low frequencies but also in high frequency regions. Apart from the moments at s = 0 (DC), this method uses shifted moments as well. This property provides the necessary information about all the frequency range. This approach requires the solution of the circuit matrix at several frequency points that are determined by the complex frequency hopping technique.

In this paper, we present the results of a simulation program implementing the multi-point Padé approximation. The program is implemented in C++ language running on UNIX and it uses the moment matching algorithms proposed earlier (Çelik *et al.* 1995). We compare the run-times as well as the accuracies with conventional simulators. In the next three sections, we introduce the theoretical background of the work. Beginning from § 5, we present the simulations and computational results on several examples.

#### 2. Order reduction

Consider a linear network which contains linear lumped components, and arbitrary linear subnetworks. The subnetworks may contain distributed elements. The MNA matrix equations of the network can be written as

$$W\frac{\mathrm{d}}{\mathrm{d}t}z(t) + Hz(t) + \sum_{k=0}^{N_{s}} D_{k}I_{k} = bu(t)$$

(1)

where z(t) is the node voltage vector including independent voltage source currents and linear inductor currents, W is the matrix for frequency dependent lumped components, H is the matrix for frequency independent lumped components, h is the vector for independent sources, h is the selector matrix that maps h, the currents entering subnetworks, and h is the input function. For the subnetworks we have

$$A_k V_k + B_k I_k = 0 \quad \text{for } k = 1, \dots, N_s$$

(2)

Writing the Laplace transform of the equations we obtain

$$\begin{bmatrix} sW + H & D_1 & D_2 & \dots & D_{N_s} \\ A_1D_1^{\mathsf{T}} & B_1 & 0 & \dots & 0 \\ A_2D_2^{\mathsf{T}} & 0 & B_2 & \dots & 0 \\ \vdots & \vdots & \vdots & \ddots & \vdots \\ A_{N_s}D_{N_s}^{\mathsf{T}} & 0 & 0 & \dots & B_{N_s} \end{bmatrix} \begin{bmatrix} Z(s) \\ I_1(s) \\ I_2(s) \\ \vdots \\ I_{N_s}(s) \end{bmatrix} = \begin{bmatrix} b \\ 0 \\ 0 \\ \vdots \\ 0 \end{bmatrix} U(s)$$

(3)

We call the MNA matrix T(s), the vector of unknowns x(s), and the excitation vector w

$$T(s)x(s) = w (4)$$

Let the output be a linear combination of the unknowns

$$H(s) = d^{\mathrm{T}}x(s) \tag{5}$$

If the elements of the system matrix T(s) are polynomials, then the solution of the system of (4) and (5) will give

$$H(s) = \frac{\sum a_i s^i}{\sum b_j s^j}$$

In methods using order reduction, the aim is to find an approximate  $\hat{H}(s)$ , which has similar frequency characteristics as the original circuit

$$\hat{H}(s) = \frac{b_0 + b_1 s + \dots + b_{q-1} s^{q-1}}{1 + a_1 s + \dots + a_q s^q}$$

#### 3. Frequency shifted moments

The system response vector  $x(s) = T^{-1}(s)w$ , can be written in a Taylor series form around  $s = s_k$

$$x(s) = \sum_{k=0}^{\infty} x_{ki}(s - s_k)^i$$

where

$$x_{ki} = \frac{\frac{\partial^{i}}{\partial s^{i}} \left[ T^{-1} \right]_{s=s_{k}}^{i} w}{i!}$$

$$x_{k0} = T^{-1}(s_{k})w$$

$$x_{ki} = -T^{-1}(s_{k}) \sum_{i}^{i} \frac{T^{(r)}(s_{k}) x_{k(i-r)}}{r!}$$

(6)

where  $T^{(r)}$  stands for the *r*th derivative of the *T* matrix with respect to *s*. The details of these equations are described elsewhere (Çelik *et al.* 1995, Tang and Nakhla 1992). The frequency shifted moments of the output are obtained from the moment vectors  $x_{ki}$  using the linear equation  $m_{ki} = d^T x_{ki}$ . So we obtain

$$H(s) = m_{k0} + m_{k1}(s - s_k) + m_{k2}(s - s_k)^2 + \cdots$$

### 4. Multi-point moment matching

In moment matching methods, the coefficients  $b_i$  and  $a_i$  satisfying (7) are found

$$\hat{H}(s) = \frac{b_0 + b_1 s + \dots + b_{q-1} s^{q-1}}{1 + a_1 s + \dots + a_q s^q}$$

$$= m_{k0} + m_{k1} (s - s_k) + m_{k2} (s - s_k)^2 + \dots + m_{k(n_{k-1})} (s - s_k)^{n_{k-1}}$$

(7)

where  $n_k$  is the number of moments calculated at  $s = s_k$ .

In the AWE method, moments evaluated at  $s_k = 0$  and  $s_k = \infty$  are used to calculate the unknown coefficients. The Markov parameters are the derivative moments and they increase the accuracy of the transient simulation (Huang *et al.* 1990).

The complex frequency hopping (CFH) technique uses the fact that when the series is truncated the function is well-approximated only around the expansion point (Chiprout and Nakhla 1994). For each expansion point the moments are matched to a ratio of polynomials, the poles and residues are found. The poles

are marked accurate if they are obtained at two different expansion points. The poles closer to the corresponding expansion points are then marked accurate. The obtained poles and corresponding residues define the system transfer function uniquely.

In the following section, we describe the method for calculation of the coefficients  $b_i$  and  $a_i$  directly from the moments.

#### 4.1. Calculation of coefficients

For each expansion point  $s = s_k$  we have the following equation

$$\frac{b_0 + b_1 s + \dots + b_p s^p}{1 + a_1 s + \dots + a_\theta s^q} = m_{k0} + m_{k1} \hat{s} + \dots + m_{k(n_{k-1})} \hat{s}^{n_{k-1}}$$

(8)

where  $\hat{s} = s - s_k$ .

If we rewrite the left-hand side of (8) we obtain

$$\hat{a}_{i} = \sum_{k=1}^{q} a_{l} \binom{l}{i} s_{k}^{l-i}, \quad i = 0, 1, \dots, q, \quad a_{0} = 1$$

$$\hat{b}_{i} = \sum_{k=1}^{p} b_{l} \binom{l}{i} s_{k}^{l-i}, \quad i = 0, 1, \dots, p$$

(9)

There are  $n_k$  constraints for choosing p + q + 1 unknowns. This gives the equation  $\hat{b} = B\hat{a}$ , where

$$\hat{b} = \begin{bmatrix} \hat{b}_{0} \\ \hat{b}_{1} \\ \vdots \\ \hat{b}_{n_{k-1}} \end{bmatrix} \quad \hat{a} = \begin{bmatrix} \hat{a}_{0} \\ \hat{a}_{1} \\ \vdots \\ \hat{a}_{n_{k-1}} \end{bmatrix} \quad B = \begin{bmatrix} m_{k0} \\ m_{k1} & m_{k0} \\ \vdots & \vdots & \ddots \\ m_{k(n_{k-1})} & m_{k(n_{k-2})} & \dots & m_{k0} \end{bmatrix}$$

We form the  $C_p$  and  $C_q$  matrices and the  $M_k$  matrix

$$M_k = [C_{p1} : C_{p2} : C_{p3} : - BC_{q2} : - BC_{q3}]$$

The C<sub>n</sub> matrix can be defined as

$$C_{n} \equiv \begin{bmatrix} C_{n1} & C_{n2} & C_{n3} \end{bmatrix}$$

$$= \begin{bmatrix} 1 & s_{k} & s_{k}^{2} & s_{k}^{3} & \cdots & s_{k}^{n-1} & s_{k}^{n} & s_{$$

The solution of the equation

$$\mathbf{M}_{k} \begin{bmatrix} b_{0} \\ b_{1} \\ \vdots \\ b_{p} \\ a_{1} \\ a_{2} \\ \vdots \\ a_{q} \end{bmatrix} = \begin{bmatrix} m_{k0} \\ m_{k1} \\ \vdots \\ m_{k(n_{k}-1)} \end{bmatrix}$$

$$(11)$$

will give the unknown coefficients.

If there is more than one expansion point, the equations will be solved simultaneously. Therefore, the coefficients are extracted according to the information obtained from all expansion points. This method can also be extended for the solution of the system in the least squares sense. In the literature (Çelik *et al.* 1995) the solution for p = q - 1 is explained in detail.

#### 5. Simulations and computational results

The method presented above will be discussed here according to numerical and practical concepts. The simulator we designed performs the following tasks:

- (i) parsing the input file;

- (ii) forming the circuit matrix;

- (iii) calculation of frequency shifted moments according to the recursive scheme given in (6) and in the literature (Tang and Nakhla 1992);

- (iv) repetition of last step for each expansion point;

- (v) matching moments to an approximating rational and extracting the coefficients.

Since the lower-upper (LU) factorization of the circuit matrix is known from the solution of the first moment vector, higher order moments are obtained by one forward and one backward substitution (FBS) only. If the number of the expansion points is n + 1, we have a total of (n + 1) LU factorizations of the circuit matrix. Obtaining the AC response of the circuit at DC + n points includes (n + 1) LUs and  $\sum_{i=0}^{n} n_i$  FBSs where  $n_i$  is the number of moments at the ith expansion point.

# 5.1. Selection of the expansion points

Since we are employing a form of Padé approximation and searching for an approximating rational, only the dominant poles are crucial in our design. In time and frequency analyses, the poles closer to the  $j\omega$  axis are important, therefore we choose expansion points on the  $j\omega$  axis. Once we set our frequency range of interest, we can apply the CFH technique. The frequency range of interest is generally between DC and a maximum frequency ( $\approx$  1 GHz in interconnect circuits). The CFH technique finds the expansion points by a binary search algorithm. This algorithm first performs the single point expansions at s=0 and  $s=j\omega_{\rm max}$  and looks for common poles of these two expansions. If any common pole is found, it is marked as an accurate pole, otherwise a third expansion point is selected between these two

points. The binary search continues until every two successive points have at least one common pole. The CFH technique gives not only the expansion points, but also the number of moments for each expansion point. We use this information in our method and obtain the multi-point Padé approximation function.

#### 5.2. Extracting the coefficients

The coefficients of the approximating function are obtained from a system of matrix equations (11). Each  $M_k$  and  $m_k$  element has its complex conjugate row in matrix equations. Therefore, this  $N \times N$  complex matrix system is equivalent to an  $N \times N$  real system of equations and can be solved using ordinary elimination algorithms such as LU (Conte and de Boor 1981). To overcome the accuracy problems we employ double precision arithmetic and frequency scaling in our simulations. A problem in the method is the stability of approximations. As a consequence of using Padé approximation, our technique may generate spurious right-hand side poles. Even so, in most cases, the unstable poles disappear when increasing the order of approximation.

#### 6. Examples

Several examples are presented here to demonstrate the performance of the method. In run-time measurements, a SUN-SPARC20 machine running SunOS 4.1.3 is used and the averages of several run-times are given.

## 6.1. Example 1

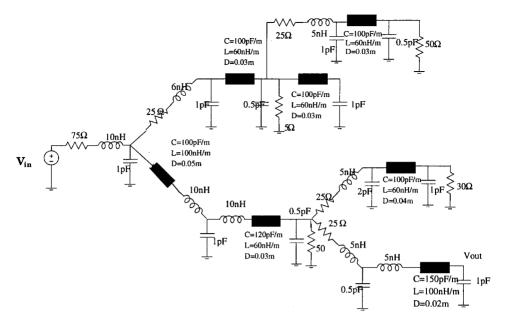

The first example is an interconnect circuit given by Çelik *et al.* (1995), Tang and Nakhla (1992). As seen from Fig. 1, the circuit has 29 lumped components, seven lossless transmission lines and 21 nodes. Our frequency range of interest is 0–6 GHz. By applying the CFH technique to this circuit, we found the order of approximation to be 35. The expansion points and moment numbers are given in Table 1. The AC response of the circuit was computed according to the moment table.

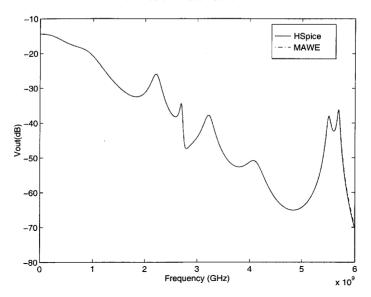

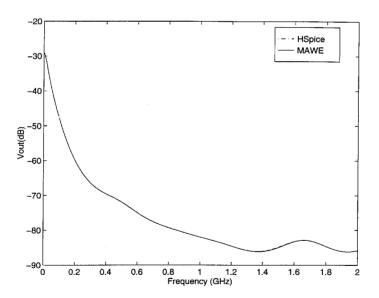

The AC response H(s) of the circuit and the time comparisons are shown in Fig. 2 and Table 2, respectively. The I/O times are excluded in Table 2. As seen from the figure, multi-point Padé approximation (MAWE) and HSpice responses match each other exactly. We can see from Table 2 that MAWE took much less time to get the same results as HSpice and Spice3. When we calculate the AC response at 6000 points in the frequency range 0–6 GHz, the proposed MAWE computes nearly 11 times faster than HSpice and nearly seven times faster than Spice3. In a 600 point AC analysis, HSpice and Spice3 run times are closer to that of MAWE, but still MAWE has three or four times better scores.

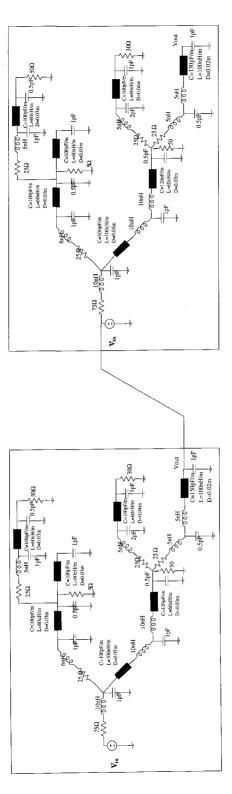

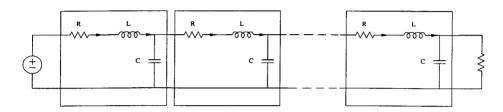

# 6.2. Example 2

The second example consists of two cascaded blocks, where the previous circuit is taken as a block (Fig. 3). The circuit has twice as many elements and nodes, i.e. 42 nodes, 14 lossless transmission lines and 58 lumped components. We applied frequency scaling as in the first example. The expansion points and number of moments for this circuit are given in Table 3. Since this circuit is more complex and more stiff

Figure 1. Interconnect model with seven transmission lines.

| Expansion point                        | Moments |  |

|----------------------------------------|---------|--|

| s = 0                                  | 10      |  |

| $s = 2\pi 1.25 \times 10^9 \text{j}$   | 10      |  |

| $s = 2\pi 2.50 \times 10^9 \text{j}$   | 10      |  |

| $s = 2\pi 5.00 \times 10^9 \mathrm{j}$ | 10      |  |

Table 1. Expansion points and moment numbers for interconnect network

Figure 2. Output waveform for interconnect network.

|                          | Real analysis time (s) |                   |                     |                   |  |

|--------------------------|------------------------|-------------------|---------------------|-------------------|--|

|                          | Interconnect Cct.      |                   | Cascaded Int. Cct.  |                   |  |

| Simulator                | 6000 pts               | 600 pts           | 6000 pts            | 600 pts           |  |

| MAWE<br>HSPICE<br>SPICE3 | 1·1<br>11·9<br>7·8     | 0·9<br>3·7<br>2·4 | 1·6<br>21·9<br>11·0 | 1·5<br>4·9<br>4·2 |  |

Table 2. Timing results for interconnect networks (I/O times excluded).

| Expansion point                      | Moments |  |  |

|--------------------------------------|---------|--|--|

| s = 0                                | 10      |  |  |

| $s = 2\pi 1.00 \times 10^9 j$        | 5       |  |  |

| $s = 2\pi 2 \cdot 00 \times 10^9 j$  | 4       |  |  |

| $s = 2\pi 2.50 \times 10^9 j$        | 3       |  |  |

| $s = 2\pi 3.00 \times 10^9 \text{j}$ | 5       |  |  |

| $s = 2\pi 4.00 \times 10^9 \text{j}$ | 5       |  |  |

| $s = 2\pi 5.00 \times 10^9 j$        | 5       |  |  |

| $s = 2\pi 5.50 \times 10^9 j$        | 2       |  |  |

| $s = 2\pi 6.00 \times 10^9 j$        | 5       |  |  |

Table 3. Expansion points and moment numbers for cascaded interconnects.

than the other one, we need to spread the expansion points to eight points. The order of approximation increased as well, i.e. we now compute a total of 78 moments.

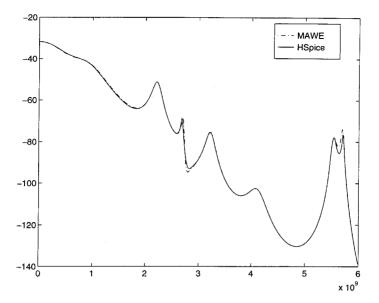

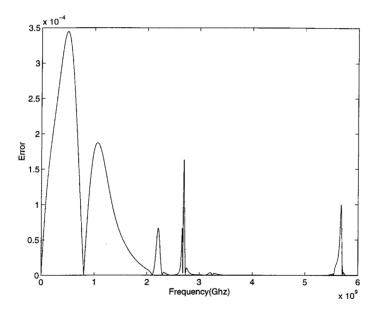

The AC response of cascaded interconnects computed by MAWE are compared with HSpice in Fig. 4. One can notice a slight difference between two plots only around 3 GHz and 6 GHz. This slight error is acceptable since the absolute error never exceeds  $3.5 \times 10^{-4}$  (Fig. 5).

The time comparison is given in Table 2 where the I/O times are excluded. MAWE still has a significant speed advantage over HSpice and Spice3. This time, the speed up over HSpice is 14 times and over Spice3 is seven times.

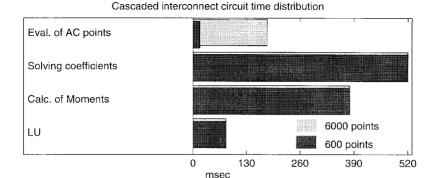

We were expecting the simulator to become faster as the circuit enlarges. However, as in this example, when the circuit size is doubled, the speed gain over Spice simulators do not have a noticeable change. When we investigate the time distribution in Fig. 6, we notice a remarkable time consumption for solving coefficients according to formula 11 and moment update according to formula 6. In this example, the matrix solver consumed the biggest time because of the high approximation order and too many expansion points. This results in a large and ill-conditioned moment matrix system that takes a long time to solve.

Figure 3. Cascaded interconnects with 14 transmission lines.

Figure 4. AC Response of MAWE in cascaded interconnects circuit.

Figure 5. Absolute error of MAWE response in cascaded interconnects circuit.

#### 6.3. *Example* 3

Next, we will consider two RLC circuits in the same topology with 10 cells and 100 cells as given in Fig. 7. The circuits have 10 RLC elements with 21 nodes and 100 RLC elements and 201 nodes respectively. The frequency range of interest in the first circuit is 0–5 Hz, while 0–2 Hz in the second one. Scaling was applied to element

Figure 6. Timing analysis for cascaded interconnects circuit.

Figure 7. Blocks that form the RLC circuits with 21 and 201 nodes.

values as  $1 \times 10^9$ . The moment numbers and expansion points are given in Table 4. It can be seen that, the 28th order approximation is needed to find the response of the 201-node circuit, while only the 20th order is sufficient for the 21-node circuit.

The output responses of two circuits are given in Figs 8 and 9. We can see that the exact response of HSpice is matched by MAWE for both circuits. The time comparisons for both RLC circuits are given in Table 5. In RLC20, MAWE's run

|       | Expansion point                                                                                                   | Moments        |

|-------|-------------------------------------------------------------------------------------------------------------------|----------------|

| (a)   | $\begin{cases} s = 0 \\ s = 2\pi 2.50 \times 10^9 \text{j} \\ s = 2\pi 5.00 \times 10^9 \text{j} \end{cases}$     | 12<br>7<br>7   |

| (b) : | $\begin{cases} s = 0 \\ s = 2\pi 1.00 \times 10^{9} \text{j} \\ s = 2\pi 2.00 \times 10^{9} \text{j} \end{cases}$ | 16<br>10<br>10 |

Table 4. Expansion points and moment numbers for (a) 21- and (b) 201-node RLC circuits.

Figure 8. AC Response of the RLC circuit with 21 nodes.

Figure 9. AC Response of the RLC circuit with 201 nodes.

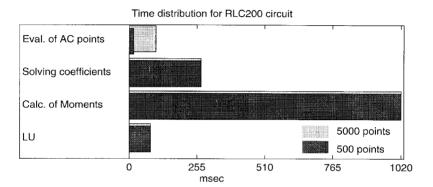

time improvement against HSpice is of the order of 30, while in RLC200 the improvement is higher. This indicates that MAWE has better scores in a big analysis such as 5000 points or more. This is valid not only for RLC circuits, but also interconnect circuits with distributed components. When we look at time distributions in Fig. 10, the addition of the moment update process is easily noticed. In contrast to Example 2, the moment update takes a longer time than solving coefficients in this example. This is because of the huge circuit matrix which is used in (6).

|                          | Real analysis time (s) |                    |                    |                    |

|--------------------------|------------------------|--------------------|--------------------|--------------------|

|                          | RLC with 21 nodes      |                    | RLC with 201 nodes |                    |

| Simulator                | 5000 pts               | 500 pts            | 5000 pts           | 500 pts            |

| MAWE<br>HSPICE<br>SPICE3 | 0·4<br>12·5<br>20·4    | 0·25<br>5·4<br>1·1 | 2·6<br>89<br>19    | 2·5<br>12·9<br>2·4 |

Table 5. Timing results for RLC networks (I/O times excluded).

Figure 10. Timing analysis for RLC circuit with 201 nodes.

The sum of multiplications at one expansion point is  $O(n_i^2 \times n^2)$ , where n is the size of the circuit matrix T and  $n_i$  is the number of moments at one expansion point.

Consequently, in large circuits with large matrices, the moment update process dominates the run time, while in moderate circuits with many expansion points and high approximation orders, the coefficient's solving time becomes dominant in total time. As the circuits expand, the addition of LU on total time will increase; however, this will not cause dramatic changes in total execution time, since LU is performed once at each expansion point.

#### 7. Conclusions

We have introduced a program for verifying the AC response of linear circuits, using multi-point moment matching techniques. Instead of calculating the frequency response at a large number of discretized points, like conventional simulators do, our program extracts the coefficient of an *s*-domain approximating rational of the impulse response. The program can handle RLC. circuits as well as circuits with lossless transmission lines with no topological constraints, such as inductor loops, etc. Verification of the pole–zero analysis can also be done by the proposed program. The execution time of the MAWE program compared with Spice-like simulators is 8–10 times better. This improvement can be multipled by using a better matrix

solver. The performance of the simulator increases as the matrix solver's execution time decreases. Hence, MAWE will have better run-time advances against Spice-like simulators by means of a faster solver than we have used. This program can also handle multi-conductor transmission line circuits by using an approach presented by Tang and Nakhla (1992). Finally, our simulator can perform transient analysis of larger networks easily because of the nature of transient analysis which requires lower order approximation (4)–(8). The recovery of the execution time will also be similar to AC analysis.

#### REFERENCES

- Anastakis, D. F., Gopal, N., Kim, S. Y., and Pillage, L. T., 1993, On the stability of approximations in asymptotic waveform evaluation. *Proceedings of the Design Automation Conference*, May.

- Bracken, J. E., Raghavan, V., and Rohrer, R. A., 1992, Interconnect simulation with asymptotic waveform evaluation. *IEEE Transactions on Circuits and Systems-I: Fundamental Theory and Applications*, **39**, 869–878.

- CONTE, S. D., and DE BOOR, C., 1981, Elementary Numerical Analysis (Singapore: McGraw-Hill).

- Celik, M., 1994, Fast Algorithms for linear and nonlinear microwave circuit simulation, Ph.D. thesis, July, Bilkent University.

- Celik, M., Ocali, O., Tan, M. A., and Atalar, A., 1995, Pole-zero computation in microwave circuits using multi point Pade approximation. *IEEE Transactions on Circuits and Systems-I: Fundamental Theory and Applications*, **42**, 6–13.

- CHIPROUT, E., and NAKHLA, M. S., 1994, Asymptotic Waveform Evaluation and Moment Matching for Interconnect Analysis (Boston, Massachusetts, U.S.A.: Kluwer Academic); 1995, Analysis of interconnect networks using Complex Frequency Hopping (CFH). IEEE Transactions on Computer Aided Design of Integrated Circuits and Systems, 14, 186–200.

- Feldmann, P., and Freund, R. W., 1995, Efficient Linear Circuit Analysis via the Lanczos Process. *IEEE Transactions on Computer Aided Design of Integrated Circuits and Systems*, 14, 639–649.

- Huang, X., Raghavan, V., and Rohrer, R. A., 1990, AWESim: a program for the efficient analysis of linear(ized) circuits. *Technical Digest of the International Conference on Computer-Aided Design (ICCAD)*, November, pp. 534–537.

- PILLAGE, L. T., and ROHRER, R. A., 1990, Asymptotic waveform evaluation for timing analysis. *IEEE Transactions on Computer Aided Design of Integrated Circuits and Systems*, 9, 352–366.

- TANG, T. K., and NAKHLA, M. S., 1992, Analysis of high-speed VLSI interconnects using the asymptotic waveform evaluation technique. *IEEE Transactions on Computer Aided Design of Integrated Circuits and Systems*, 11, 341–352.