## Low temperature thin film transistors with hollow cathode plasma-assisted atomic layer deposition based GaN channels

S. Bolat, C. Ozgit-Akgun, B. Tekcan, N. Biyikli, and A. K. Okyay

Citation: Applied Physics Letters 104, 243505 (2014); doi: 10.1063/1.4884061

View online: http://dx.doi.org/10.1063/1.4884061

View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/104/24?ver=pdfcov

Published by the AIP Publishing

## Articles you may be interested in

Electronic and optical device applications of hollow cathode plasma assisted atomic layer deposition based GaN thin films

J. Vac. Sci. Technol. A 33, 01A143 (2015); 10.1116/1.4903365

Fabrication of AlN/BN bishell hollow nanofibers by electrospinning and atomic layer deposition APL Mat. **2**, 096109 (2014); 10.1063/1.4894782

Optical characteristics of nanocrystalline AlxGa1-xN thin films deposited by hollow cathode plasma-assisted atomic layer deposition

J. Vac. Sci. Technol. A 32, 031508 (2014); 10.1116/1.4870381

Crystal AIN deposited at low temperature by magnetic field enhanced plasma assisted atomic layer deposition J. Vac. Sci. Technol. A **31**, 01A114 (2013); 10.1116/1.4764112

Changes in the growth mode of low temperature GaN buffer layers with nitrogen plasma nitridation of sapphire substrates

Appl. Phys. Lett. 71, 1228 (1997); 10.1063/1.119859

## Low temperature thin film transistors with hollow cathode plasma-assisted atomic layer deposition based GaN channels

S. Bolat, <sup>1,2,a)</sup> C. Ozgit-Akgun, <sup>2,3</sup> B. Tekcan, <sup>1,2</sup> N. Biyikli, <sup>2,3</sup> and A. K. Okyay <sup>1,2,3,a)</sup> <sup>1</sup>Department of Electrical and Electronics Engineering, Bilkent University, Ankara 06800, Turkey <sup>2</sup>UNAM, National Nanotechnology Research Center, Bilkent University, Ankara 06800, Turkey <sup>3</sup>Institute of Materials Science and Nanotechnology, Bilkent University, Ankara 06800, Turkey

(Received 25 April 2014; accepted 4 June 2014; published online 18 June 2014)

We report GaN thin film transistors (TFT) with a thermal budget below 250 °C. GaN thin films are grown at 200 °C by hollow cathode plasma-assisted atomic layer deposition (HCPA-ALD). HCPA-ALD-based GaN thin films are found to have a polycrystalline wurtzite structure with an average crystallite size of 9.3 nm. TFTs with bottom gate configuration are fabricated with HCPA-ALD grown GaN channel layers. Fabricated TFTs exhibit n-type field effect characteristics. N-channel GaN TFTs demonstrated on-to-off ratios (I<sub>ON</sub>/I<sub>OFF</sub>) of 10<sup>3</sup> and sub-threshold swing of 3.3 V/decade. The entire TFT device fabrication process temperature is below 250 °C, which is the lowest process temperature reported for GaN based transistors, so far. © 2014 AIP Publishing LLC. [http://dx.doi.org/10.1063/1.4884061]

GaN has earned an unrivaled popularity for high power applications and operation in harsh environments. GaN is a well-known, transparent semiconducting material with a band-gap of 3.4 eV. It is the material of choice in various applications such as high-electron-mobility transistors (HEMTs), ultraviolet light emitting devices (UV LEDs),<sup>2</sup> chemical sensors, UV photo detectors, and power amplifiers.<sup>5</sup> Currently, there are mainly two deposition techniques most widely used for the utilization of epitaxial GaN films, namely, metal organic chemical vapor deposition (MOCVD) and molecular beam epitaxy (MBE). Both of these techniques offer single crystalline films; however, both necessitate high deposition temperatures.<sup>6,7</sup> In order to utilize GaN in settings with limited thermal budget, such as back end of line (BEOL) and flexible substrates, utilization of alternative deposition techniques carries vital importance. With this aim, low-temperature deposition of GaN has been reported, where different methods such as, sputtering, pulsed laser deposition (PLD), and atomic layer deposition (ALD)<sup>10</sup> were employed. Differing from other techniques, ALD offers the most uniform and conformal deposition even at subnanometer thickness levels.11

TFTs are the driving elements of the liquid crystal display technology. <sup>12</sup> Most commonly used active material in TFT-based technologies is amorphous Si (a-Si). <sup>13</sup> However, due to low carrier mobility in a-Si, high fabrication thermal budget, and strong absorption of visible light, a-Si is not suitable for flexible and transparent electronics applications. Therefore, a-Si has been challenged by several transparent metal oxides, of which the most famous one is ZnO. <sup>14,15</sup> TFTs with ZnO active layers have been reported to have electrical characteristics similar to or even better than those with a-Si. <sup>16</sup> However, stability problem of the ZnO TFTs still remains as an important issue. To overcome this problem by the use of an alternative material as the active layer of TFTs, Chen and colleagues <sup>8</sup> demonstrated devices with

sputtered GaN channels, having a maximum process temperature of 1100 °C, which is prohibitively high for flexible electronics. Apart from their work, there are few other recent reports on the use of low-temperature deposited GaN in TFTs; however, all include high device processing temperatures, making them unsuitable for low temperature electronics. <sup>17,18</sup>

Here, we present hollow-cathode plasma-assisted atomic layer deposition (HCPA-ALD)-grown GaN based TFT with the lowest reported thermal budget so far, keeping the entire layer growth and device fabrication steps below 250 °C. Physical properties of GaN thin films and the electrical characteristics of the fabricated TFTs are discussed.

GaN thin films are deposited by HCPA-ALD, using trimethylgallium (GaMe<sub>3</sub>) as the Ga precursor and  $N_2/H_2$  gas mixture (50/50 sccm) with 300 W of plasma power as the N precursor at a process temperature of 200 °C. Grazing-incidence X-ray diffraction (GIXRD) measurements were carried out in a PANalytical X'Pert PRO MRD diffractometer using Cu  $K_{\alpha}$  radiation, where the crystallite size of the thin film is calculated by the line profile analysis (LPA) method. Chemical composition of the GaN thin film is determined by X-ray photoelectron spectroscopy (XPS) using Thermo Scientific K-Alpha spectrometer with a monochromatized Al  $K_{\alpha}$  X-ray source.

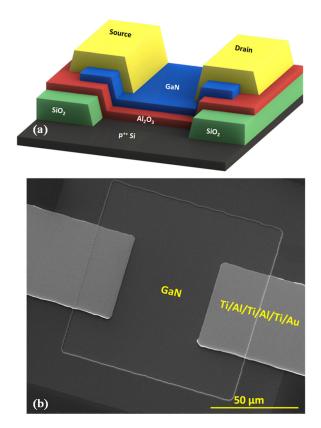

A 3-dimensional depiction of the proposed TFT is shown in Fig. 1(a), and a scanning electron microscope (SEM) image of the top view of the device is shown in Fig. 1(b). Fabrication of the bottom gate TFT starts with the RCA cleaning of the highly doped (1–5 m $\Omega$ -cm) p-type Si wafer. Plasma-enhanced chemical vapor deposition of a 200–nm-thick SiO<sub>2</sub> is performed at 250 °C. The SiO<sub>2</sub> film is patterned to define the active device areas. An HF-last clean is immediately followed by the growth of 77-nm-thick Al<sub>2</sub>O<sub>3</sub> and 11-nm-thick GaN subsequently deposited at a single ALD process in a modified Fiji F200-LL ALD Reactor (Ultratech/Cambridge NanoTech Inc.), where the process temperature is kept at 200 °C. Active device areas are isolated by Ar-based dry etching of the GaN layer. Source and

a) Authors to whom correspondence should be addressed. Electronic addresses: bolat@ee.bilkent.edu.tr and aokyay@ee.bilkent.edu.tr

FIG. 1. (a) 3D schematic of the HCPA-ALD-based GaN TFT, (b) SEM image of the fabricated device.

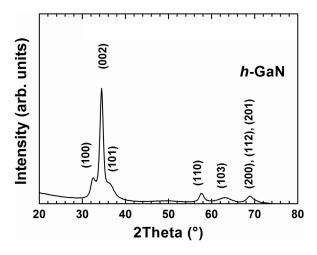

FIG. 2. GIXRD pattern of the HCPA-ALD-grown GaN thin film, which reveals a polycrystalline wurtzite crystal structure.

drain contacts are formed by sputtering a multilayer metal stack consisting of Ti/Al/Ti/Al/Ti/Au (30/30/30/30/30/60 nm) as suggested in Ref. 19. In order to keep the thermal budget of the device fabrication as low as possible, no annealing is applied after the contact metallization step. Fabricated TFTs have W/L=1 with L=50  $\mu$ m. Electrical measurements of the devices are performed using Keithley 4200 semiconductor parameter analyzer.

The GIXRD pattern of the HCPA-ALD-grown GaN is shown in Fig. 2. Diffraction peaks obtained from the measurement, which correspond to wurtzite (hexagonal) crystal structure, reveal the polycrystalline nature of the deposited GaN thin film. The average crystallite size of the polycrystalline wurtzite GaN film is extracted from the (002) reflection and found to be 9.3 nm. <sup>10</sup> Chemical composition of the GaN thin film is obtained by making use of XPS with depth profile analysis, and 42.24 at. % Ga, 54.57 at. % N, 1.65 at. % O, and 1.54 at. % Ar are detected in the film after 60 s of Ar ion etching. Overestimation of the N content is observed due to the contribution of the Ga Auger peaks, which overlap with the N 1 s peak. <sup>10</sup>

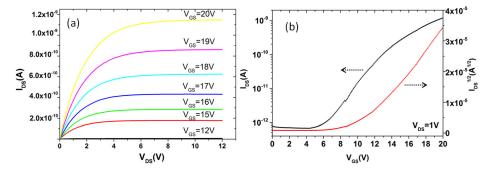

Output electrical characteristics of the HCPA-ALDbased GaN TFTs are shown in Fig. 3(a). Fabricated devices have clear pinch-off and saturation characteristics, and they exhibit n-type field effect transistor behavior. Transfer characteristics of the devices with  $V_{DS} = 1 \text{ V}$  applied are shown in Fig. 3(b). Fabricated TFT has an  $I_{ON}/I_{OFF}$  ratio of  $2 \times 10^3$ . The advantage of using a thick gate insulator is that the gate leakage current was kept below 0.5 pA for all the bias conditions. The threshold voltage of the device is extracted from the transfer characteristics (using  $\sqrt{I_{DS}}$ ), and it is found to be 11.8 V. Sub-threshold swing (SS) of the device is generally influenced by trap states located in the forbidden gap. Extracted SS of the fabricated device is 3.3 V/decade. Charge mobility in the channel is extracted in the linear region of the device operation ( $V_{GS} = 20 \text{ V}$  and  $V_{DS} = 1 \text{ V}$ ) by using the equation given in (1), where Cox is the gate oxide capacitance per unit area. Relative permittivity of the ALD based Al<sub>2</sub>O<sub>3</sub>, required to calculate C<sub>ox</sub>, is obtained from a previous study. 20 Calculated effective charge mobility in the channel is 0.025 cm<sup>2</sup>/V-sec. This particularly low mobility can be attributed to the nanocrystalline structure of the HCPA-ALD based GaN thin films, and the surface states at the semiconductor insulator interface

$$\mu = \frac{I_{DS} \times L}{W \times C_{OX} \times \left( (V_{GS} - V_{TH}) \times V_{DS} - \frac{V_{DS}^2}{2} \right)}.$$

(1)

FIG. 3. (a) Output, and (b) transfer characteristics of the HCPA-ALD-based GaN TFTs.

FIG. 4. Threshold shift vs. positive gate bias stress (2.5 MV/cm).

To further analyze the effect of trapped charges in the operation of the devices, effect of the positive gate bias stress on the threshold voltage is investigated, and the results are shown in Fig. 4. Prior to each stress cycle, devices are characterized by acquiring their transfer curves. A 2.5 MV/cm field is applied between the gate and source/drain of the TFTs while both drain and the source are kept at 0 V. Following the stress cycle, the transfer characteristics of the devices are obtained again. The difference in the threshold voltages between these measurements is recorded as the threshold voltage shift. Threshold voltage shift reveals the presence of charge trap states at the insulator semiconductor interface and or within the Al<sub>2</sub>O<sub>3</sub> dielectric layer. As seen in Fig. 4, threshold voltage shifts to higher values with longer applied positive gate bias stress. This is due to increased number of trapped electrons which screen the applied gate field resulting in an increased threshold voltage. However, the increase in the threshold voltage after 1000s of bias stress is smaller than that of high performance TFTs based on ZnO channels.<sup>21</sup>

In conclusion, GaN TFTs, with the lowest thermal budget to date, are fabricated with the utilization of HCPA-ALD method. Deposited GaN thin film is shown to have polycrystalline wurtzite structure with a crystallite size of 9.3 nm using GIXRD and LPA, respectively. Elemental analysis of the films revealed the low amount of oxygen in HCPA-ALD based GaN thin films. Output characteristics of the TFTs are obtained which show that the fabricated devices exhibit n-type enhancement mode field effect transistor behavior with clear pinch-off and saturation characteristics. Transfer characteristics of the devices show that the fabricated transistors have on-to-off ratios of  $2 \times 10^3$ . Finally, the effect of the positive gate bias stress on threshold voltage of the devices is studied, and reasonable threshold voltage shifts for a device with a considerably thick gate insulator are obtained. This study demonstrates the possibility of using low-temperature ALD-grown GaN layers for alternative and stable flexible/transparent TFT devices upon further materials and process optimization.

This work was supported by the Scientific and Technological Research Council of Turkey (TUBITAK), Grant Nos. 109E044, 112M004, 112E052, 112M482, and

113M815. N.B. acknowledges support from European Union FP7 Marie Curie International Reintegration Grant (NEMSmart, Grant No. PIRG05-GA-2009-249196). A.K.O. acknowledges support from European Union FP7 Marie Curie International Reintegration Grant (PIOS, Grant No. PIRG04-GA-2008-239444). S.B. acknowledges TUBITAK-BIDEB for national M.Sc. fellowship. Authors thank Berk Berkan Turgut for the SEM image.

- <sup>1</sup>P. Parikh, U. K. Mishra, and Y. F. Wu, "AlGaN/GaN HEMTs—An overview of device operation and applications," Proc. IEEE **90**(6), 1022–1031 (2002).

- <sup>2</sup>J. K. Sheu, S. J. Chang, C. H. Kuo, Y. K. Su, L. W. Wu, Y. C. Lin, W. C. Lai, J. M. Tsai, G. C. Chi, and R. K. Wu, "White-light emission from near UV InGaN-GaN LED chip precoated with blue/green/red phosphors," IEEE Photonics Technol. Lett. 15(1), 18–20 (2003).

- <sup>3</sup>S. J. Pearton, B. S. Kang, S. Kim, F. Ren, B. P. Gila, C. R. Abernathy, J. Lin, and S. N. G. Chu, "GaN-based diodes and transistors for chemical, gas, biological and pressure sensing," J. Phys.: Condens. Matter **16**(29), R961 (2004).

- <sup>4</sup>D. Walker, E. Monroy, P. Kung, J. Wu, M. Hamilton, F. J. Sanchez, J. Diaz, and M. Razeghi, "High-speed, low-noise metal-semiconductor-metal ultraviolet photodetectors based on GaN," Appl. Phys. Lett. **74**(5), 762–764 (1999).

- <sup>5</sup>K. Joshin, T. Kikkawa, H. Hayashi, T. Maniwa, S. Ydkokawa, M. Yokoyama, N. Adachi, and M. Takikawa, presented at the IEEE International Electron Devices Meeting, IEDM '03 Technical Digest, 2003.

- <sup>6</sup>S. Nakamura, Y. Harada, and M. Seno, "Novel metalorganic chemical vapor deposition system for GaN growth," Appl. Phys. Lett. **58**(18), 2021–2023 (1991).

- <sup>7</sup>E. J. Tarsa, B. Heying, X. H. Wu, P. Fini, S. P. DenBaars, and J. S. Speck, "Homoepitaxial growth of GaN under Ga-stable and N-stable conditions by plasma-assisted molecular beam epitaxy," J. Appl. Phys. **82**(11), 5472–5479 (1997).

- <sup>8</sup>R. Chen, W. Zhou, and H. S. Kwok, "Top-gate thin-film transistors based on GaN channel layer," Appl. Phys. Lett. 100(2), 022111 (2012).

- <sup>9</sup>A. Kobayashi, S. Kawano, Y. Kawaguchi, J. Ohta, and H. Fujioka, "Room temperature epitaxial growth of m-plane GaN on lattice-matched ZnO substrates," Appl. Phys. Lett. **90**(4), 041908 (2007).

- <sup>10</sup>C. Ozgit-Akgun, E. Goldenberg, A. K. Okyay, and N. Biyikli, "Hollow cathode plasma-assisted atomic layer deposition of crystalline AlN, GaN and Al<sub>x</sub>Ga<sub>1-x</sub>N thin films at low temperatures," J. Mater. Chem. C 2 (12), 2123–2136 (2014).

- <sup>11</sup>M. Ritala and M. Leskela, "Atomic layer deposition," in *Handbook of Thin Film Materials* (Academic Press, San Diego, CA, 2001), Vol. 1, p. 103.

- <sup>12</sup>R. A. Street, "Thin film transistors," Adv. Mater. **21**(20), 2007–2022 (2009).

- <sup>13</sup>R. A. Street, Technology and Applications of Amorphous Silicon (Springer, 2000).

- <sup>14</sup>U. Ozgur, Ya. I. Alivov, C. Liu, A. Teke, M. A. Reshchikov, S. Doğan, V. Avrutin, S.-J. Cho, and H. Morkoç, "A comprehensive review of ZnO materials and devices," J. Appl. Phys. 98(4), 041301 (2005).

- <sup>15</sup>E. M. C. Fortunato, P. M. C. Barquinha, A. C. M. B. G. Pimentel, A. M. F. Gonçalves, A. J. S. Marques, L. M. N. Pereira, and R. F. P. Martins, "Fully transparent ZnO thin film transistor produced at room temperature," Adv. Mater. 17(5), 590–594 (2005).

- <sup>16</sup>R. L. Hoffman, B. J. Norris, and J. F. Wager, "ZnO-based transparent thinfilm transistors," Appl. Phys. Lett. 82(5), 733–735 (2003).

- <sup>17</sup>R. Chen, W. Zhou, M. Zhang, and H. S. Kwok, "Bottom-gate thin-film transistors based on GaN active channel layer," IEEE Electron Device Lett. **34**(4), 517–519 (2013).

- <sup>18</sup>C. Liu, S. Liu, S. Huang, and K. J. Chen, "Plasma-enhanced atomic layer deposition of AlN epitaxial thin film for AlN/GaN heterostructure TFTs," IEEE Electron Device Lett. 34(9), 1106–1108 (2013).

- <sup>19</sup>L. Pang and K. Kim, "Improvement of Ohmic contacts to n-type GaN using a Ti/Al multi-layered contact scheme," Mater. Sci. Semicond. Process. (published online).

- <sup>20</sup>M. D. Groner, F. H. Fabreguette, J. W. Elam, and S. M. George, "Low-temperature Al<sub>2</sub>O<sub>3</sub> atomic layer deposition," Chem. Mater. 16(4), 639–645 (2004).

- <sup>21</sup>R. B. M. Cross and M. M. De Souza, "Investigating the stability of zinc oxide thin film transistors," Appl. Phys. Lett. 89(26), 263513 (2006).