## Plasma-enhanced atomic layer deposition of amorphous $\text{Ga}_2\text{O}_3$ gate dielectrics

Yosef Badali <sup>a,\*</sup>, Engin Arslan <sup>b,c</sup>, Turkan Gamze Ulusoy Ghobadi <sup>d</sup>, Suleyman Ozcelik <sup>e</sup>, Ekmel Ozbay <sup>c,f,g</sup>

<sup>a</sup> Department of Computer Engineering, Istanbul Ticaret University, 34840, Istanbul, Turkey

<sup>b</sup> Department of Electrical and Electronics Engineering, Antalya Bilim University, 07190, Antalya, Turkey

<sup>c</sup> Nanotechnology Research Center, Bilkent University, 06800, Ankara, Turkey

<sup>d</sup> National Nanotechnology Research Center, Bilkent University, 06800, Ankara, Turkey

<sup>e</sup> Department of Physics, Faculty of Sciences, Gazi University, Ankara, Turkey

<sup>f</sup> Department of Electrical and Electronics Engineering, Bilkent University, 06800, Ankara, Turkey

<sup>g</sup> Department of Physics, Bilkent University, 06800, Ankara, Turkey

### ARTICLE INFO

#### Keywords:

Atomic layer deposition

Amorphous  $\text{Ga}_2\text{O}_3$

Dielectric properties

Interface traps

### ABSTRACT

Amorphous gallium oxide ( $\text{Ga}_2\text{O}_3$ ) thin films were investigated as gate dielectrics for electronic device applications using plasma-enhanced atomic layer deposition. The structural and morphological properties as well as the electrical and dielectric behaviors of  $\text{Ga}_2\text{O}_3$  thin films were explored. The surface morphology of the amorphous  $\text{Ga}_2\text{O}_3$  thin film was highly smooth with root mean square of 0.55 nm and low defect density, which were visible to atomic force microscopy. The grazing incidence X-ray diffraction pattern showed no discernible peak, indicating that the film was amorphous. The X-ray photoelectron spectroscopy depth-profiling analysis showed that the Ga/O ratio was 0.76, slightly more than the optimum 2/3 ratio (0.67). The temperature-dependent current–voltage characteristics of the Au/Ni/ $\text{Ga}_2\text{O}_3$ /p-Si structure revealed that ideality factor and barrier height values decreased and increased with increasing temperature, respectively, demonstrating their high temperature dependency. Regardless of the applied frequency,  $\text{Ga}_2\text{O}_3$  thin films exhibited a good dielectric constant of about ~9 at zero bias voltage. The comprehensive capacitance–voltage analysis showed low trap densities of about  $10^{12} \text{ eV}^{-1} \text{ cm}^{-2}$  at the  $\text{Ga}_2\text{O}_3$ –p-Si interface.

### 1. Introduction

Gate dielectrics have been researched for passivating surfaces, suppressing leakage current while improving breakdown strengths, and providing effective electrostatic control of the gate. Different high-k materials have been investigated as possible dielectric layers, including  $\text{Al}_2\text{O}_3$ ,  $\text{Y}_2\text{O}_3$ ,  $\text{HfO}_2$ , and  $\text{TiO}_2$  [1–4]. These high-k materials, however, often require post-deposition annealing and may crystallize or react with the underlying Si substrate which is undesirable. Crystalline gallium oxide ( $\beta$ - $\text{Ga}_2\text{O}_3$ ) is a transparent conducting oxide with an ultra-wide bandgap of 4.9 eV, whereas amorphous  $\text{Ga}_2\text{O}_3$  is only an electrical insulator because the combination of an ultra-wide bandgap and an amorphous structure makes electronic conduction extremely difficult. Amorphous  $\text{Ga}_2\text{O}_3$  with the characteristics of wide bandgap, high dielectric constant, and perfect thermal stability causes a reduction

of the direct tunneling leakage current [5]. Moreover, since the crystallization process in this material takes place at high temperatures, its passivation property is not lost during the deposition process at low temperatures. It has also been reported that the doped and undoped  $\text{Ga}_2\text{O}_3$  amorphous structure significantly reduces the interfacial density states and leakage current when used as a gate dielectric in electronic devices [6–9]. These characteristics make  $\text{Ga}_2\text{O}_3$  excellent as a dielectric material in next generation applications. The structure and electrical behavior of  $\text{Ga}_2\text{O}_3$  thin films should, therefore, be routinely studied as dielectric layers, and their applicability to the manufacturing process should be defined for semiconductor devices. However, the dielectric properties of  $\text{Ga}_2\text{O}_3$  structures have not yet been studied in detail.

So far, various growth processes, such as metal–organic chemical vapor deposition, molecular beam epitaxy, chemical bath deposition, and atomic layer deposition (ALD), have been used to create  $\text{Ga}_2\text{O}_3$  thin

\* Corresponding author.

E-mail address: [ybedeli@ticaret.edu.tr](mailto:ybedeli@ticaret.edu.tr) (Y. Badali).

films [10–12]. Of these, ALD stands out because of its low temperature deposition and three-dimensional conformal deposition resulting from a self-limiting surface reaction and the superior regulation of thickness. Use of ALD can also ensure greater step coverage over substrates with large aspect ratios, which is necessary for a reliable dielectric gate [12]. Plasma-enhanced ALD (PEALD) technology has the advantage of extending the ALD process window toward lower temperatures by improving the chemical reaction [13]. For metal/oxide/semiconductor (MOS) applications, the use of  $\text{Ga}_2\text{O}_3$  grown with PEALD could be the right option for a dielectric gate, since non-annealed  $\text{Ga}_2\text{O}_3$  obtained by this method is an amorphous material with a high- $k$  value ( $>9$ ) and a comparatively wide bandgap ( $\sim 4.8$  eV) [14]. The PEALD-grown  $\text{Ga}_2\text{O}_3$  dielectric layers also improve the crystallization temperature, decrease the interfacial oxide layer growth at the substrate–dielectric interface, and provide good interfacial dependability with the substrate [14].

It is critical to thoroughly investigate the charge-transport properties of amorphous  $\text{Ga}_2\text{O}_3$ -based MOS devices to effectively realize high-quality devices. In recent years, there have been many endeavors to manufacture Schottky structures with a  $\text{Ga}_2\text{O}_3$  interface layer and to investigate their electrical characteristics at ambient temperature [15–17]. Unfortunately, the current–voltage ( $I$ – $V$ ) characteristics at ambient temperature do not give comprehensive information on charge-transport processes or the Schottky barrier interface's nature; however, investigations of temperature-dependent  $I$ – $V$  behaviors are useful in this regard [18]. Understanding the dielectric properties of  $\text{Ga}_2\text{O}_3$  interfaces is crucial for creating functional MOS devices. Thin films of  $\text{Ga}_2\text{O}_3$  have been investigated as promising dielectric material for a variety of device applications, including deep-ultraviolet transparent films, dielectric coatings for solar cells, dielectric gates for MOS devices, and high-temperature sensors, due to their wide bandgap and good chemical and thermal stability [19]. Nevertheless, there are few detailed reports on the dielectric properties of amorphous  $\text{Ga}_2\text{O}_3$  [20, 21].

In the present paper, we deposit  $\text{Ga}_2\text{O}_3$  thin films on p-Si substrate to fabricate the MOS structure, and we explore the surface morphology and composition as well as the electrical and dielectric properties. The charge-transport mechanisms of this structure are studied using temperature-dependent  $I$ – $V$  characteristics for 80–300 K. In addition, the dielectric behavior of the fabricated MOS structure is explored using frequency-dependent capacitance–voltage ( $C$ – $V$ ) and conductance–voltage ( $G/\omega$ – $V$ ) experiments. To better understand the characteristics of the  $\text{Ga}_2\text{O}_3$ –p-Si interfaces, the interface trap density ( $D_{it}$ ) is estimated using admittance spectroscopy at ambient temperature.

## 2. Device structure and fabrication process

Deposition of the amorphous  $\text{Ga}_2\text{O}_3$  thin film was implemented by PEALD system (Okyay ALD) using TEG ( $(\text{C}_2\text{H}_5)_3\text{Ga}$ ) and  $\text{O}_2$  plasma as precursors on  $6\text{ mm} \times 6\text{ mm}$  dimensional p-Si substrates. The growth process was begun by setting the reactor temperature and vacuum line temperature as 240 and 200 °C, respectively. An radio-frequency coil with an alternate radio-frequency power of 250 W was used to create the remote  $\text{O}_2$  plasma. There were four stages in each ALD cycle: (1) TEG pulse, (2) Ar purge, (3)  $\text{O}_2$  plasma, and (4) Ar purges. The films were deposited at a base pressure of  $\sim 5 \times 10^{-4}$  bar and 250 °C. As a result of these stages, nominally 30-nm thick  $\text{Ga}_2\text{O}_3$  film was grown on p-Si substrate verified using a spectroscopic ellipsometer (Jobin Yvon-Horiba).

Prior to the growth process, a 300-nm aluminum (Al) metal contact was put on the back side of the p-Si substrate. In order to form the ohmic contact, samples were annealed at 480 °C for 10 min in an  $\text{N}_2$  atmosphere with rapid thermal annealing equipment. After the growth process, 1-mm diameter circular dot Schottky contact formation was carried out on the  $\text{Ga}_2\text{O}_3$  thin film surface, using 100- and 50-nm thick nickel (Ni) and gold (Au), respectively.

## 3. Results and discussion

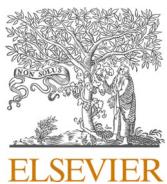

The grazing incidence X-ray diffraction (GIXRD) must be characterized to prove that the  $\text{Ga}_2\text{O}_3$  thin film is amorphous. The GIXRD results of the  $\text{Ga}_2\text{O}_3$  thin film show no discernible peak, indicating that the film is amorphous (Fig. 1a). The surface morphology of the amorphous  $\text{Ga}_2\text{O}_3$  thin film grown on p-Si substrate, investigated using atomic force microscopy (AFM) imaging over a  $3\text{ }\mu\text{m} \times 3\text{ }\mu\text{m}$  scan size to demonstrate its surface quality, shows that the amorphous  $\text{Ga}_2\text{O}_3$  has a crack-free, mirror-like surface form, and a smooth surface morphology with low roughness (root mean square = 0.55 nm) and low defect density (Fig. 1b).

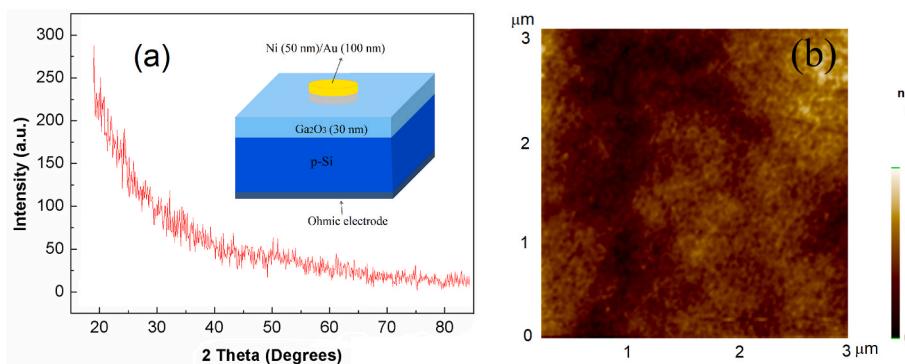

X-ray photoelectron spectroscopy (XPS, Thermo Fisher Scientific, Al K-radiation,  $h = 1486.6$  eV) in survey mode utilizing the flood gun for surface charge neutralization with 30 eV pass energy and 0.1 eV step size is used to investigate the surface elemental composition and binding energy (BE) values. Keeping the aliphatic C1s component at  $284.8 \pm 0.1$  eV and adjusting other peaks in the spectra correspondingly is used to calibrate the BE scale. Depth-profiling is by using XPS with  $\text{Ar}^+$  ions with 1000 eV energy. The samples' depth profiles are created in 14 cycles with a cycle duration of 20 s each.

The O1s and Ga3d spectra of the sample in both bulk and surface areas are shown in Fig. 2a–d. The O1s spectra in the surface is deconvoluted into two peaks: the sharp peak corresponding to low energy centered at 530.5 eV and a weak one corresponding to high energy centered at 532.4 eV. The peak at 530.5 eV is associated with Ga–O bond species. The peak at 532.4 eV is attributed to Ga–hydroxide bonds, such as  $\text{OH}^-$  or  $\text{H}_2\text{O}$  on the film surface. However, in the bulk medium, the O1s has a single peak response, showing successful growth of the  $\text{Ga}_2\text{O}_3$  layer. In addition, emergence of the highly intense peaks at 20.25 eV (Fig. 2b and d) confirms the presence of Ga–O bonds, i.e. the creation of a  $\text{Ga}_2\text{O}_3$  thin film. The O2s core level is a faint peak at higher (23.50 eV) BE [22]. Moreover, Ga3d orbitals have similar spectra for both surface and bulk regions. For a better qualitative comparison, the depth profile is extracted for the sample. The Ga:O ratio is calculated using data from the Ga3d and O1s core levels, as well as carbon concentrations (C1s data). The calculated Ga/O ratio is 0.76 (Fig. 2e), which is slightly more than the ideal ratio of 2/3 (0.67). This deviation from the ideal ratio indicates the presence of both Ga interstitial and O vacancies [22]. Moreover, the carbon contamination is only present in the surface and near surface regions. Therefore, the XPS depth-profiling analysis clearly shows the successful growth of the  $\text{Ga}_2\text{O}_3$  layer. It should be mentioned that the purge time during the ALD growth cycle should be optimized to avoid introduction of carbon residues in grown metal oxide.

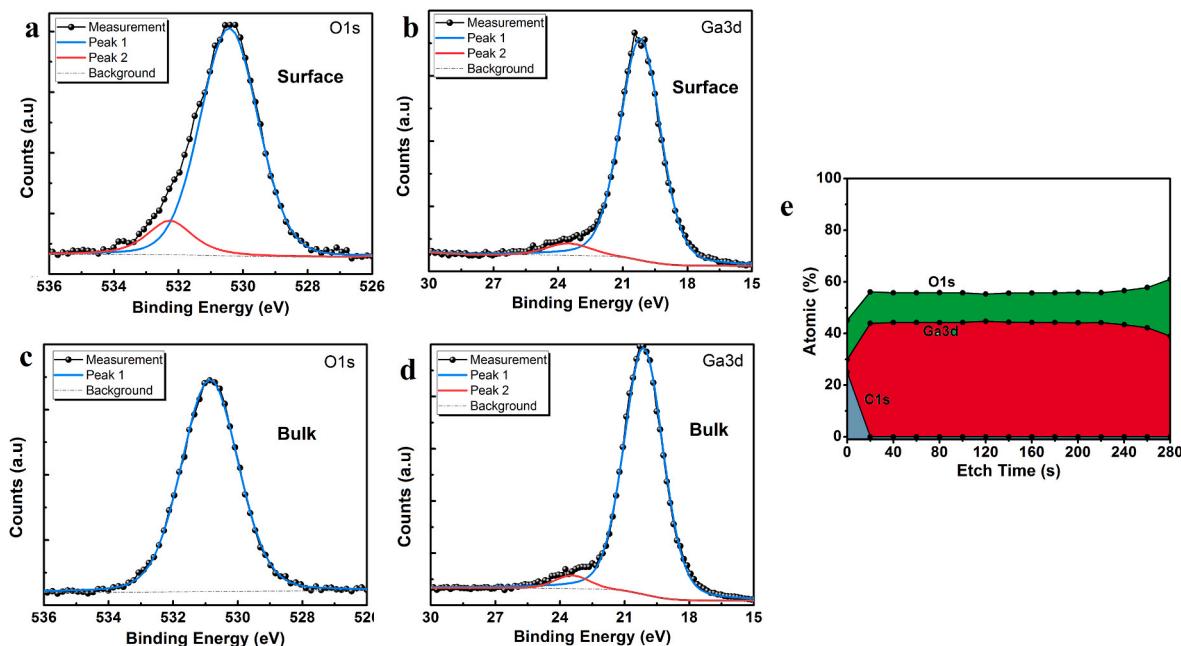

Fig. 3a shows the semilogarithmic  $I$ – $V$  measurements of the Au/Ni/ $\text{Ga}_2\text{O}_3$ /p-Si structure recorded at 80–320 K in 20 K increments. The structure shows an exponential increase in forwarding bias current with a modest change in leakage current on the applied reverse bias, regardless of temperature, which is a characteristic property of a rectifying interface. The leakage current density at  $-2$  V reverse bias changes from  $2.4 \times 10^{-6}$  to  $1.7 \times 10^{-3}$   $\text{A cm}^{-2}$ , when temperature increases from 80 to 320 K (inset, Fig. 3a). These relatively remarkable leakage currents can be attributed to native oxides between the  $\text{Ga}_2\text{O}_3$ –p-Si interface and to the presence of both Ga interstitial and O vacancies. The slope and y-axis intercept of the  $\ln(I)$ – $V$  plots are used to determine the ideality factor ( $n$ ) and barrier height ( $\Phi_{b0}$ ) for each temperature, with respect to thermionic emission theory [23, 24]. When the temperature increases from 80 to 320 K,  $n$  and  $\Phi_{b0}$  values change from 11.4 to 2.2 and 0.28–0.74 eV, respectively (Fig. 3b). That is, with increasing temperature, the  $n$  and  $\Phi_{b0}$  values decrease and increase, respectively, demonstrating their high temperature dependency. However, the manufactured Au/Ni/ $\text{Ga}_2\text{O}_3$  structure has a relatively high  $\Phi_{b0}$  and low leakage current at 300 K, indicating a good-quality Ni Schottky contact created on the  $\text{Ga}_2\text{O}_3$  in the current configuration. It also shows that the  $\text{Ga}_2\text{O}_3$  layer has a good amorphous structure and exhibits an effective passivation feature. Barrier inhomogeneities at the Ni/ $\text{Ga}_2\text{O}_3$  boundary

**Fig. 1.** (a) Grazing incidence X-ray diffraction (GIXRD) patterns, inset is a schematic of Au/Ni/Ga<sub>2</sub>O<sub>3</sub>/p-Si structure and (b) AFM image (3  $\mu$ m  $\times$  3  $\mu$ m scans) of the amorphous Ga<sub>2</sub>O<sub>3</sub> layer deposited on p-Si substrate.

**Fig. 2.** XPS spectra of (a) O1s and (b) Ga3d for the Ga<sub>2</sub>O<sub>3</sub> film surface, and (c) O1s and (d) Ga3d for the Ga<sub>2</sub>O<sub>3</sub> thin film bulk. (e) Atomic percentage of elements Ga, O, and C in the  $\sim$ 30-nm thick amorphous Ga<sub>2</sub>O<sub>3</sub> thin film obtained via XPS depth profiles. Total etching time of 280 s.

might explain the temperature-dependent characteristics of  $n$  and  $\phi_{b0}$ . The thermionic emission model considers the metal–semiconductor interface, which is atomically flat and geometrically homogeneous. The Schottky barriers of a variety of metal–semiconductor complexes, however, are rarely homogeneous. A multitude of physical factors can create barrier inhomogeneity. These include poor interface quality, non-stoichiometries of the diffusion region, non-uniformity of the interlayer charge density, non-uniformity of the interface layer thickness, and doping atom distribution pattern. A local non-uniform Schottky barrier consists of substantially low and high  $\phi_{b0}$  regions of nanoscale size, which are expected to be dispersed according to a Gaussian distribution. Because the current predominantly passes through the patches with a low  $\phi_{b0}$  at lower temperatures, the patches with a high  $n$  dominate the current. However, at high temperatures, the current tends to pass through patches with a high  $\phi_{b0}$ , resulting in decreased  $n$  and increased  $\phi_{b0}$  [25,26].

An explanatory potential fluctuation model based on barrier height inhomogeneity with patchy contacts at the metal–semiconductor interface can clarify the abnormalities observed in  $\phi_{b0}$  and  $n$ . For contacts with patches with lateral dimensions less than the depletion width, the thermionic emission mechanism might still be efficacious [18]. As a

result of the interface barrier being non-homogeneous, the barrier is not fixed, but instead complies with Gaussian distribution with different mean barrier height ( $\bar{\phi}_{b0}$ ) and standard deviation ( $\sigma_0$ ) values. As a result, the dependency of  $\phi_{b0}$  on temperature may be deduced in terms of non-uniform Schottky contact using a Gaussian distribution of the barrier height with  $\bar{\phi}_{b0}$  and  $\sigma_0$ , with apparent barrier height ( $\phi_{ap}$ ) and ideality factor ( $n_{ap}$ ) provided as follows [27–30]:

$$\phi_{ap} = \bar{\phi}_{b0} - \frac{q\sigma_s^2}{2kT} \quad (1)$$

$$\frac{1}{n_{ap}(T)} - 1 = -\rho_2 + \frac{q\rho_3}{2kT} \quad (2)$$

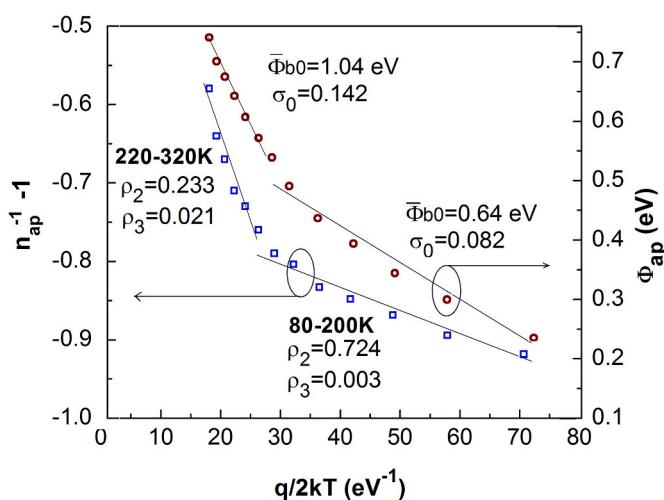

where  $\rho_2$  and  $\rho_3$  are temperature-dependent voltage coefficients that characterize the voltage deformation of the Schottky barrier height distributions. Plots of  $\phi_{ap}$  and  $1/n_{ap} - 1$  vs  $q/2kT$  (Fig. 4) are derived using equations (1) and (2). In the 80–200 and 220–320 K temperature ranges, the  $\phi_{ap}$  and  $1/n_{ap} - 1$  vs  $q/2kT$  plots clearly reveal two linear regimes, showing a double Gaussian distribution of barrier heights. In the plot of  $\phi_{ap}$  vs  $q/2kT$ , the linear fit of the data's y-axis intercept and slope provide  $\bar{\phi}_{b0}$  and  $\sigma_0$ , with values of 0.64 eV and 0.082 for 80–200 K,

**Fig. 3.** (a) The temperature-dependent semi-log  $I$ - $V$  characteristics in an experimental setting, inset is leakage current density vs temperature of the Au/Ni/Ga<sub>2</sub>O<sub>3</sub>/p-Si structure. (b) The  $\Phi_{b0}$  and  $n$  vs temperature plots determined for Au/Ni/Ga<sub>2</sub>O<sub>3</sub>/p-Si structure.

**Fig. 4.** The  $\Phi_{ap}$  and  $1/n_{ap} - 1$  vs  $q/2 kT$  plots of Au/Ni/Ga<sub>2</sub>O<sub>3</sub>/p-Si structure.

respectively, and correspondingly 1.04 eV and 0.142 for 220–320 K. The  $\sigma_0$  value denotes the degree of barrier homogeneity such that smaller  $\sigma_0$  indicates a more homogenous Schottky barrier created in the interface. The  $\sigma_0$  values for the 80–200 and 220–320 K temperature ranges are not small enough to be insignificant compared to  $\bar{\Phi}_{b0}$ , suggesting the presence of non-homogeneous barrier height. Two linear regions are visible on the plot of  $1/n_{ap} - 1$  vs  $q/2 kT$ , indicating the occurrence of double barrier height distribution. The y-axis intercept and slope of the linear fitted line of  $1/n_{ap} - 1$  vs  $q/2 kT$  plot are  $\rho_2$  and  $\rho_3$ , respectively. For the range of 80–200 K,  $\rho_2 = 0.724$  and  $\rho_3 = 0.003$  are found, whereas in the range of 220–320 K,  $\rho_2 = 0.233$  and  $\rho_3 = 0.021$ . The  $1/n_{ap} - 1$  vs  $q/2 kT$  plot's linear nature suggests that the  $n$  values might be represented by the voltage deformation of barrier height Gaussian distribution.

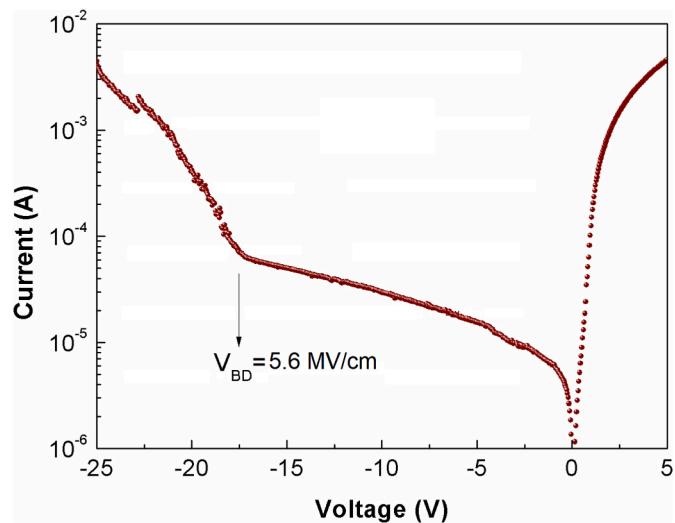

The Ga<sub>2</sub>O<sub>3</sub> is well-known for having a high breakdown voltage ( $V_{BD}$ ), making it suited for high-temperature applications. The  $I$ - $V$  plots are for room temperature between –25 and 5 V to determine the  $V_{BD}$  for a 30-nm amorphous Ga<sub>2</sub>O<sub>3</sub> thin film. The calculated  $V_{BD}$  is 5.6 MV cm<sup>–1</sup> (Fig. 5). In the literature, for a similar Ga<sub>2</sub>O<sub>3</sub> MIS structure, breakdown voltages of 7 MV cm<sup>–1</sup> have been reported [31]. The resulting relatively low breakdown voltage and remarkable leakage current can be attributed to native oxides between the Ga<sub>2</sub>O<sub>3</sub>-p-Si interface and attributed to the presence of both Ga interstitial and O vacancies.

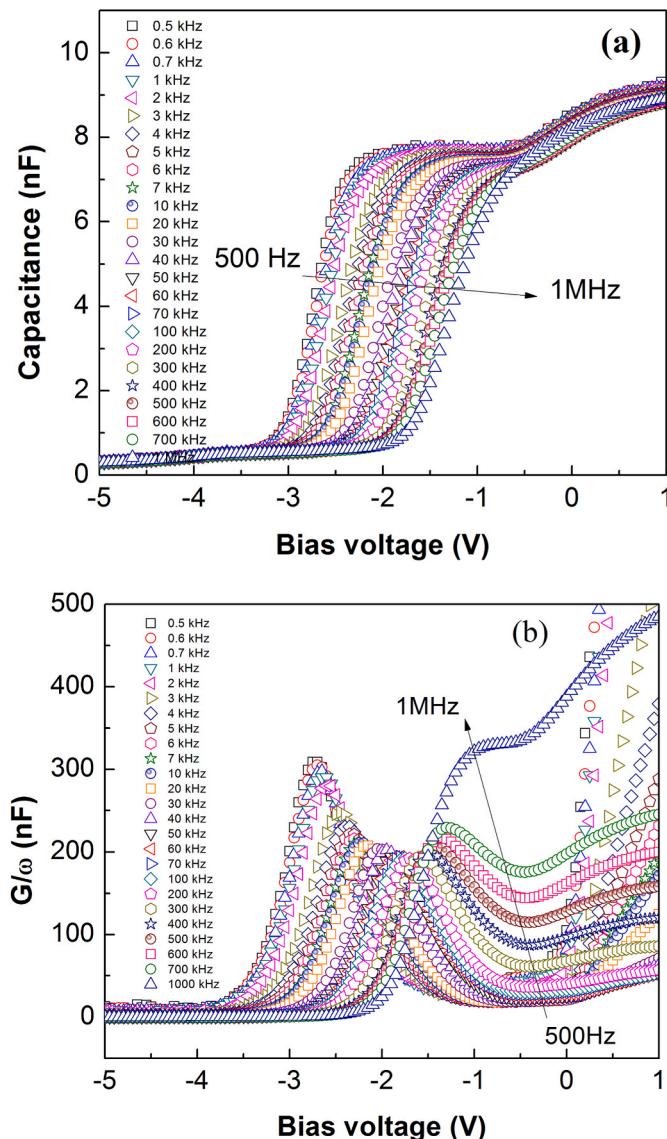

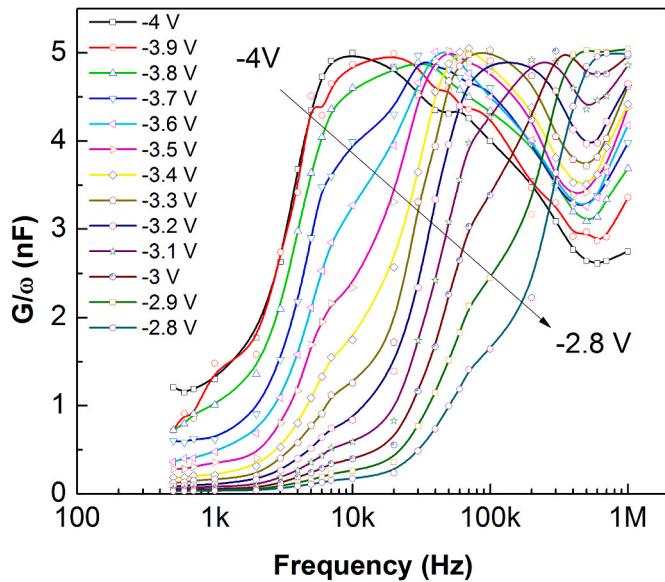

The  $C$ - $V$  and  $G/\omega$ - $V$  measurements conducted at various frequencies between 500 Hz and 1 MHz using an HP 4192A LF impedance analyzer are used to investigate the dielectric behavior and trapping effects of the amorphous Ga<sub>2</sub>O<sub>3</sub> layer. The frequency-dependent  $C$ - $V$  and  $G/\omega$ - $V$  plots of the Au/Ni/Ga<sub>2</sub>O<sub>3</sub>/p-Si structure at ambient temperature are shown in Fig. 6a and b. The  $C$ - $V$  plots clearly reveal the typical operating modes of ideal MIS systems, such as inversion, depletion, and accumulation and show similar behavior to a typical MOS capacitor [29,30]. For negative bias voltage less than –3 V, an inversion layer of electrons forms at the interface. Capacitance overshoot at the start of inversion is regularly seen in  $C$ - $V$  plots and thought to be due to the oxide's trapping centers filling up. With decreasing frequency, the  $C$ - $V$  plots shift to a more negative gate bias (Fig. 6a). At ambient temperature, the interface traps are closer to the valence band, explaining the horizontal shift. At lower frequencies, more traps are effective in charge build-up; therefore, to compensate for the charge due to interface traps, more negative gate biases are required at lower frequencies for the same band bending in the semiconductor, creating a horizontal shift in the  $C$ - $V$ . However, for various frequencies, the maximum capacitance values are fairly close to one another, at about 8 nF. Although these frequency-dependent  $C$ - $V$

**Fig. 5.** Semilogarithmic  $I$ - $V$  curve of the Au/Ni/Ga<sub>2</sub>O<sub>3</sub>/p-Si structure at room temperature. The breakdown voltage was 5.6 MV cm<sup>–1</sup>.

**Fig. 6.** Measured frequency-dependent (a)  $C$ – $V$  and (b)  $G/\omega$ – $V$  plots of the  $\text{Au}/\text{Ni}/\text{Ga}_2\text{O}_3/\text{p-Si}$  structure at ambient temperature.

curves are not like those of the MIS stack made of various dielectric alloys, research studies show that MIS structures prepared with  $\text{Ga}_2\text{O}_3$  show similar frequency-dependent behavior [31]. This unusual behavior shows that the  $\text{Ga}_2\text{O}_3$  layer formed on p-Si has low interface traps. Otherwise, these interfacial traps can greatly increase their capacitance values at low frequencies because they can easily follow AC signals at these frequencies, resulting in a significant increase in the differential capacitance maximum value between low and high frequencies. The additional kink near  $-0.5$  V is attributed to the interface traps located between p-Si substrate and  $\text{Ga}_2\text{O}_3$  insulator layers. The nonideal MIS capacitance curve might undergo a parallel shift from the ideal curve because of the flat band voltage, fixed charge, oxide trapped charge, interface trapped charge, and mobile oxide charge effects [31]. The  $G/\omega$ – $V$  plots give a peak for each frequency in the depletion region, and these peak values also shift to more negative bias voltage regions at lower frequencies (Fig. 6b) similar to the shifts seen in the  $C$ – $V$  plots due to interface traps. In addition, significantly larger frequency dispersion in  $C$ – $V$  and  $G/\omega$ – $V$  curves are evident in the trend, especially in the accumulation region. The frequency dispersion seen in accumulation might be due to a low-resistance oxide layer next to the interface rather than a large density of interface states at the conduction band edge [32].

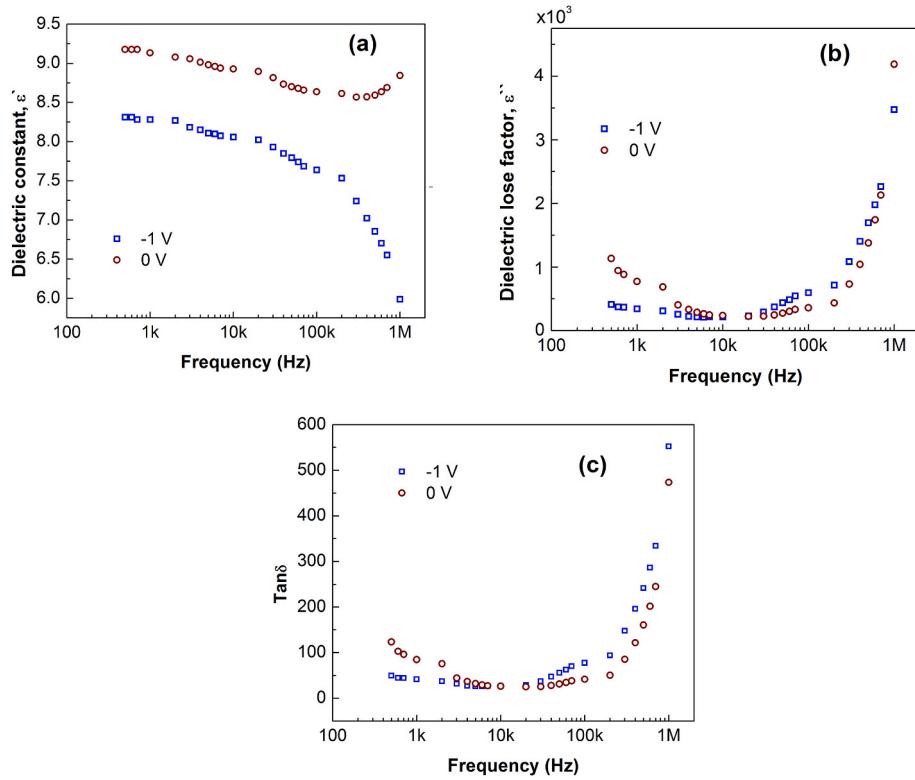

The dielectric constants of the  $\text{Au}/\text{Ni}/\text{Ga}_2\text{O}_3/\text{p-Si}$  structure are computed as a function of frequency (500 Hz–1 MHz) using the following formula:

$$\epsilon' = \frac{C}{C_0} = \frac{Cd}{\epsilon_0 A} \quad (3)$$

where  $\epsilon_0$  is the vacuum permittivity equal to  $8.854 \times 10^{-14} \text{ F cm}^{-1}$  and  $C$ ,  $d$ , and  $A$  are the measured capacitance, thickness, and area of the specimen, respectively. The imaginary part of the permittivity ( $\epsilon''$ ) or loss factor and dissipation factor ( $\tan \delta$ ) are given as follows:

$$\epsilon'' = \frac{G}{\omega C_0} = \frac{Gd}{\epsilon_0 A \omega} \quad (4)$$

$$\tan \delta = \frac{\epsilon''}{\epsilon'} \quad (5)$$

where  $G$  is the measured conductance and  $\omega$  is the angular frequency. The loss factor is the energy lost in the dielectric due to frictional damping, which prevents the bound charge's displacement from remaining in phase with field changes. The frequency-dependent real ( $\epsilon'$ ) and imaginary ( $\epsilon''$ ) parts of the dielectric constant at  $-1$  V and zero bias used to study the dielectric characteristic of the  $\text{Au}/\text{Ni}/\text{Ga}_2\text{O}_3/\text{p-Si}$  structure in the accumulation region are shown in Fig. 7a and b. The dielectric constant has a value of about 9 and does not change much depending on the frequency at zero bias (Fig. 7a). These dielectric values are consistent with previous research [20,31]. Traditional dielectric oxides have a dispersion behavior for  $\epsilon'$ . At low frequencies, dielectric materials have large dielectric constant values, which gradually drop as frequency increases. The extrinsic (space charge, grains, and grain borders) and intrinsic (ionic, bipolar, and electronic) contributions to dielectric polarization are responsible for a high dielectric constant at low frequencies. The relaxation of extrinsic variables causes the dielectric constant to decrease with increasing frequency. The Maxwell–Wagner type of interfacial polarization, however, may be responsible for a large dielectric constant at low frequencies [33]. In contrast to the dielectric constant, the dielectric loss factor (Fig. 7b) and  $\tan \delta$  (Fig. 7c) initially decrease with increasing frequency, reach a minimum, and then increase again as frequency increases. Actually, the minimum value of  $\epsilon'$  corresponds to the maximum value of  $\epsilon''$ . This is known as inductive behavior and is the outcome of series resistance ( $R_s$ ) and interface traps ( $D_{it}$ ) interacting with the  $\text{Au}/\text{Ni}/\text{Ga}_2\text{O}_3/\text{p-Si}$  structure [34]. In other words, the sample shows a metallic feature after a certain frequency or voltage value. The  $\tan \delta$ – $f$  plots for  $-1$  V and zero bias also exhibit U-shape behavior like the  $\epsilon''$ – $f$  plots due to the inductive behavior of the structure.

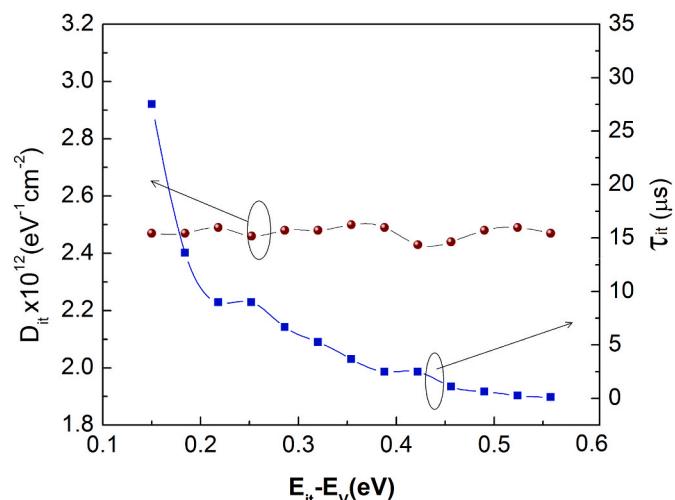

To obtain the energy density distribution profile of interface traps ( $D_{it}$ ) as well as relaxation time ( $\tau$ ) for the  $\text{Au}/\text{Ni}/\text{Ga}_2\text{O}_3/\text{p-Si}$  structure, we use the conductance method due to its higher accuracy and reliability compared to other methods such as surface admittance and high–low frequency capacitance [35]. The conductance method entails measuring  $C$  and  $G/\omega$  as a function of a number of variables, including DC bias voltage and AC voltage modulation frequency. The value of  $G/\omega$  as a function of the frequency of the applied signal is found using Eq. (6) [35,36]:

$$\frac{G_p}{\omega} = \frac{\omega C_{ox}^2 G_m}{\omega^2 (C_{ox} - C_m)^2 + G_m^2} = (qAD_{it} / 2\omega\tau) \ln(1 + \omega^2 \tau^2) \quad (6)$$

where  $\omega$  is the angular frequency ( $= 2\pi f$ ),  $C_{ox}$  is the capacitance of the interfacial oxide layer, and  $C_m$  and  $G_m$  are the measured capacitance and conductance, respectively.

The measured  $C_m$  and  $G_m/\omega$  values for varied applied bias voltages are used to generate the  $G/\omega$ – $f$  graphs (Fig. 8). These graphs show a peak for each voltage ( $G/\omega$ )<sub>max</sub>, with the peak location shifting from low to high frequency as the applied bias voltage decreases. The  $D_{it}$  is probably responsible for this peak behavior. At the peak values (Fig. 8),

Fig. 7. The (a)  $\epsilon' - f$ , (b)  $\epsilon'' - f$ , and (c)  $\tan\delta - f$  plots of the Au/Ni/Ga<sub>2</sub>O<sub>3</sub>/p-Si structure at ambient temperature.

Fig. 8. The  $G_p/\omega$  vs frequency plots at different bias voltages (-4 to -2.8 V with 0.1 V steps) for Au/Ni/Ga<sub>2</sub>O<sub>3</sub>/p-Si structure.

$d(G_p/\omega)/d(\omega\tau) = 0$  and this peak condition for Eq. (6) provides  $\omega\tau = 1.98$ . The energy of interface traps ( $E_{it}$ ) in p-type Si may be described as Eq. (7) about the top of the  $E_V$  band on the Si surface [29]:

$$E_{it} - E_V = q(\varphi_s + E_F) \quad (7)$$

where  $q$  is the electronic charge,  $\varphi_s$  is the surface potential, and  $E_F$  is the Fermi energy level. The  $D_{it}$  values are calculated via multiplying the maximum values  $(G_p/\omega)_{\max}$  by 2.5 [ $D_{it} \approx \frac{2.5}{Aq} (G_p/\omega)_{\max}$ ] and interface states relaxation time is estimated by  $\tau \approx 1.98/\omega_p$  [36]. The extracted  $D_{it}$

and its  $\tau$  values as a function of energy separation from the valence band edge are shown in Fig. 9. The values of  $D_{it}$  are  $2.43 \times 10^{12}$  to  $2.50 \times 10^{12}$  eV<sup>-1</sup>cm<sup>-2</sup> and are almost constant with energy (Fig. 9). The manufacturing of the gate dielectric and device passivation applications is well suited to such low  $D_{it}$  values. In addition, from the midgap to the band edges, the interface trapped charge lifetime varied from  $0.45 \times 10^{-6}$  to  $31.52 \times 10^{-6}$  s. These results demonstrate that, at frequencies greater than 1 MHz, the interface charges at traps cannot easily keep pace with the AC signal.

Fig. 9. The conductance technique was used to obtain  $D_{it}$  and  $\tau$  as a function of energy.

#### 4. Summary and conclusion

PEALD was used to deposit highly smooth and low-defect-density amorphous  $\text{Ga}_2\text{O}_3$  thin films as dielectric gates for electronic device applications. The XPS depth-profiling analysis showed that the ratio of Ga/O was 0.8, quite close to the ideal ratio of 2/3 (0.67). The temperature-dependent  $I$ - $V$  and frequency-dependent (500 Hz–1 MHz)  $C$ - $V$  and  $G/\omega$ - $V$  characteristics of the Au/Ni/ $\text{Ga}_2\text{O}_3$ /p-Si structure were studied for the electrical and dielectric behaviors of the amorphous  $\text{Ga}_2\text{O}_3$  thin films. The barrier inhomogeneity examined using temperature-dependent  $I$ - $V$  showed that the barrier formed by the  $\text{Ga}_2\text{O}_3$  layer was homogeneous due to a smaller value of  $\sigma_0$  and, therefore, exhibited an effective passivation feature. The  $C$ - $V$  plots shifted to a more negative gate bias with decreasing frequency due to interface traps being closer to the valence band at ambient temperature. However, for various frequencies, the maximum capacitance values were close to one another, at about 8 nF. The  $G/\omega$ - $V$  plots showed a peak for each frequency in the depletion region, and these peak values also shifted to more negative bias voltage regions at lower frequencies similar to the shifts seen in the  $C$ - $V$  plots due to interface traps. Regardless of the applied frequency,  $\text{Ga}_2\text{O}_3$  thin films exhibited a good dielectric constant of  $\sim 9$  at zero bias voltage. Moreover, at the  $\text{Ga}_2\text{O}_3$ -p-Si interface, thorough  $C$ - $V$  analysis revealed low state densities of the order of  $10^{12}$   $\text{eV}^{-1}\text{cm}^{-2}$ , which is within the acceptable range of an electronic device. Therefore, our experimental results indicate their usefulness for several dielectric gate and device passivation applications.

#### Prime novelty statement

The prime novelty of this research is the structural, electrical and dielectric properties of the  $\text{Ga}_2\text{O}_3$  thin film obtained by the plasma-enhanced atomic layer deposition (PEALD) were investigated in detail. The charge-transport mechanisms of this structure were studied using temperature-dependent current-voltage ( $I$ - $V$ ) characteristics. The dielectric behavior of the fabricated MOS structure was explored using frequency-dependent capacitance-voltage ( $C$ - $V$ ) and conductance-voltage ( $G/\omega$ - $V$ ) experiments. To better understand the characteristics of the  $\text{Ga}_2\text{O}_3$ /p-Si interfaces, the interface trap density ( $D_{it}$ ) was estimated using the admittance spectroscopy method.

#### Declaration of competing interest

The authors declare that they have no known competing financial interests or personal relationships that could have appeared to influence the work reported in this paper.

#### Data availability

The authors do not have permission to share data.

#### References

- [1] B. Feng, T. He, G. He, X. Zhang, Y. Wu, X. Chen, Z. Li, X. Zhang, Z. Jia, G. Ni, Q. Guo, Z. Zeng, S. Ding, Reduction of MOS interfacial states between  $\beta$ - $\text{Ga}_2\text{O}_3$  and  $\text{Al}_2\text{O}_3$  insulator by self-reactive etching with Ga flux, *Appl. Phys. Lett.* 118 (2021), 181602.

- [2] J.Q. Song, L.X. Qian, P.T. Lai, Effects of Ta incorporation in  $\text{Y}_2\text{O}_3$  gate dielectric of InGaZnO thin-film transistor, *Appl. Phys. Lett.* 109 (2016), 163504.

- [3] D. Biswas, M.N. Singh, A.K. Sinha, S. Bhattacharyya, S. Chakraborty, Effect of excess hafnium on  $\text{HfO}_2$  crystallization temperature and leakage current behavior of  $\text{HfO}_2$ /Si metal-oxide semiconductor devices, *J. Vac. Sci. Technol., B* 34 (2016), 022201.

- [4] R. Paily, A. DasGupta, N. DasGupta, P. Bhattacharya, P. Misra, T. Ganguli, L. M. Kukreja, A.K. Balamurugan, S. Rajagopalan, A.K. Tyagi, Pulsed laser deposition of  $\text{TiO}_2$  for MOS gate dielectric, *Appl. Surf. Sci.* 187 (2002) 297–304.

- [5] J. Kim, T. Sekiya, N. Miyokawa, N. Watanabe, K. Kimoto, K. Ide, Y. Toda, S. Ueda, N. Ohashi, H. Hiramatsu, H. Hosono, T. Kamiya, Conversion of an ultra-wide bandgap amorphous oxide insulator to a semiconductor, *NPG Asia Mater.* 9 (2017) 359.

- [6] H.Y. Shih, F.C. Chu, A. Das, C.Y. Lee, M.J. Chen, R.M. Lin, Atomic layer deposition of gallium oxide films as gate dielectrics in AlGaN/GaN metal-oxide-semiconductor high-electron mobility transistors, *Nanoscale Res. Lett.* 11 (2016) 235.

- [7] C.T. Lee, H.W. Chen, H.Y. Lee, Metal-oxide-semiconductor devices using  $\text{Ga}_2\text{O}_3$  dielectrics on n-type GaN, *Appl. Phys. Lett.* 82 (2003) 4304.

- [8] F. He, Y. Wang, Z. Lin, J. Su, J. Zhang, J. Chang, Y. Ha, Aqueous solution-deposited aluminum-gallium-oxide alloy gate dielectrics for low voltage fully oxide thin film transistors, *Appl. Phys. Lett.* 119 (2021), 112102.

- [9] F. He, Y. Qin, Y. Wang, Z. Lin, J. Su, J. Zhang, J. Chang, Y. Ha, Aqueous solution derived amorphous indium doped gallium oxide thin-film transistors, *IEEE J. Electron Devices Soc.* 9 (2021) 373–377.

- [10] K. Sasaki, M. Higashiwaki, A. Kuramata, T. Masui, S. Yamakoshi, Growth temperature dependences of structural and electrical properties of  $\text{Ga}_2\text{O}_3$  epitaxial films grown on  $\beta$ - $\text{Ga}_2\text{O}_3$  (010) substrates by molecular beam epitaxy, *J. Cryst. Growth* 392 (2014) 30–33.

- [11] F. Alema, B. Hertog, O. Ledyayev, D. Volovik, G. Thoma, R. Miller, A. Osinsky, P. Mukhopadhyay, S. Bakhshi, H. Ali, W.V. Schoenfeld, Solar blind photodetector based on epitaxial zinc doped  $\text{Ga}_2\text{O}_3$  thin film, *Phys. Status Solidi A* 214 (2017), 1600688.

- [12] J.W. Roberts, J.C. Jarman, D.N. Johnstone, P.A. Midgley, P.R. Chalker, R.A. Oliver, F.C.P. Massabuau,  $\alpha$ - $\text{Ga}_2\text{O}_3$  grown by low temperature atomic layer deposition on sapphire, *J. Cryst. Growth* 487 (2018) 23–27.

- [13] H. Knoops, T. Faraz, K. Arts, W.M.M. Kessels, Status and prospects of plasma-assisted atomic layer deposition, *J. Vac. Sci. Technol., A* 37 (2019), 030902.

- [14] Y. Zhuo, Z. Chen, W. Tu, X. Ma, Y. Pei, G. Wang,  $\beta$ - $\text{Ga}_2\text{O}_3$  versus  $\epsilon$ - $\text{Ga}_2\text{O}_3$ : control of the crystal phase composition of gallium oxide thin film prepared by metal-organic chemical vapor deposition, *Appl. Surf. Sci.* 420 (2017) 802.

- [15] E. Farzana, Z.hang, P.K. Paul, A.R. Arehart, S.A. Ringel, Influence of metal choice on (010)  $\beta$ - $\text{Ga}_2\text{O}_3$  Schottky diode properties, *Appl. Phys. Lett.* 110 (2017), 202102.

- [16] Y. Yao, R. Gangireddy, J. Kim, Electrical behavior of  $\beta$ - $\text{Ga}_2\text{O}_3$  Schottky diodes with different Schottky metals, *J. Vac. Sci. Technol., B* 35 (2017), 03D113.

- [17] J. Yang, F. Ren, M. Tadjer, S.J. Pearton, A. Kuramata,  $\text{Ga}_2\text{O}_3$  Schottky rectifiers with 1 ampere forward current, 650 V reverse breakdown and  $26.5 \text{ MW.cm}^{-2}$  figure-of-merit, *AIP Adv.* 8 (2018), 055026.

- [18] P.R. Sekhar Reddy, V. Janardhanam, K.-H. Shim, V.R. Reddy, S.-N. Lee, S.-J. Park, C.-J. Choi, Temperature-dependent Schottky barrier parameters of Ni/Au on n-type (001)  $\beta$ - $\text{Ga}_2\text{O}_3$  Schottky barrier diode, *Vacuum* 171 (2020), 109012.

- [19] G.X. Liu, F.K. Shan, J.J. Park, W.J. Lee, G.H. Lee, I.S. Kim, B.C. Shin, S.G. Yoon, Electrical properties of  $\text{Ga}_2\text{O}_3$ -based dielectric thin films prepared by plasma enhanced atomic layer deposition (PEALD), *J. Electroceram.* 17 (2006) 145–149.

- [20] L. Yuan, S. Li, G. Song, X.W. Sun, X. Zhang, Solution-processed amorphous gallium oxide gate dielectric for low-voltage operation oxide thin film transistors, *J. Mater. Sci. Mater. Electron.* 32 (2021) 8347–8353.

- [21] H.Y. Lee, T.W. Chang, C.T. Lee, AlGaN/GaN metal-oxide-semiconductor high-electron mobility transistors using  $\text{Ga}_2\text{O}_3$  gate dielectric layer grown by vapor cooling condensation system, *J. Electron. Mater.* 50 (2021) 3748–3753.

- [22] A. Mahmoodinezhad, C. Janowitz, F. Naumann, P. Plate, H. Gargouri, K. Henkel, D. Schmeißer, J.I. Flege, Low-temperature growth of gallium oxide thin films by plasma-enhanced atomic layer deposition, *J. Vac. Sci. Technol., A* 38 (2020), 022404.

- [23] E. Arslan, Y. Badali, M. Aalizadeh, S. Altindal, E. Özbay, Current transport properties of (Au/Ni)/ $\text{HfAlO}_3$ /n-Si metal-insulator-semiconductor junction, *J. Phys. Chem. Solid.* 148 (2021), 109758.

- [24] E. Arslan, S. Altindal, S. Ural, Ö.A. Kayal, M. ÖzTÜRK, E. Özbay, Thermal annealing effects on the electrical and structural properties of Ni/Pt Schottky contacts on the quaternary AlInGaN epilayer, *J. Electron. Mater.* 48 (2019) 887–897.

- [25] W. Monch, Some comments on the determination and interpretation of barrier heights of metal-semiconductor contacts, *Appl. Phys. A* 87 (2007) 359–366.

- [26] I. Jyothi, M.-W. Seo, V. Janardhanam, K.-H. Shim, Y.-B. Lee, K.-S. Ahn, C.-J. Choi, Temperature-dependent current-voltage characteristics of Er-silicide Schottky contacts to strained Si-on-insulator, *J. Alloys Compd.* 556 (2013) 252–258.

- [27] Z. Khurelbaatar, M.-S. Kang, K.-H. Shim, H.-J. Yun, J. Lee, H. Hong, S.-Y. Chang, S.-N. Lee, C.-J. Choi, Temperature dependent current-voltage characteristics of Au/n-type Ge Schottky barrier diodes with graphene interlayer, *J. Alloys Compd.* 650 (2015) 658–663.

- [28] S. Mahato, J. Puigdolers, Temperature dependent current-voltage characteristics of Au/n-Si Schottky barrier diodes and the effect of transition metal oxides as an interface layer, *Phys. B Condens. Matter* 530 (2018) 327–335.

- [29] E.H. Nicollian, J.R. Brews, *Metal Oxide Semiconductor (MOS) Physics and Technology*, Wiley, New York, 1982.

- [30] S.M. Sze, *Physics of Semiconductor Devices*, Wiley and Sons, New York, 1981.

- [31] A. Kaya, H. Mao, J. Gao, R.V. Chopdekar, Y. Takamura, S. Chowdhury, M.S. Islam, An investigation of electrical and dielectric parameters of sol-gel process enabled  $\beta$ - $\text{Ga}_2\text{O}_3$  as a gate dielectric material, *IEEE Trans. Electron. Dev.* 64 (2017) 2047–2053.

- [32] M. Passlack, M. Hong, J.P. Mannaerts, Quasistatic and high frequency capacitance-voltage characterization of  $\text{Ga}_2\text{O}_3$ -GaAs structures fabricated by in situ molecular beam epitaxy, *Appl. Phys. Lett.* 68 (1996) 1099.

- [33] C.S. Guclu, A.F. Ozdemir, A. Karabulut, A. Kokce, S. Altindal, Investigation of temperature dependent negative capacitance in the forward bias C-V characteristics of (Au/Ti)/ $\text{Al}_2\text{O}_3$ /n-GaAs Schottky barrier diodes (SBDs), *Mater. Sci. Semicond. Process.* 89 (2019) 26–31.

[34] Z.C. Shi, R.H. Fan, Z.D. Zhang, H.Y. Gong, J. Ouyang, Y.J. Bai, X.H. Zhang, L. W. Yin, Experimental and theoretical investigation on the high frequency dielectric properties of Ag/Al<sub>2</sub>O<sub>3</sub> composites, *Appl. Phys. Lett.* 99 (2011), 032903.

[35] A. Kaya, H. Tecimer, O. Vural, I.H. Tasdemir, S. Altindal, Capacitance/conductance-voltage-frequency characteristics of Au/PVC+TCNQ/p-Si structures in wide frequency range, *IEEE Trans. Electron. Dev.* 61 (2014) 584.

[36] E. Arslan, S. Butun, Y. Safak, E. Ozbay, Investigation of trap states in AlInN/AlN/GaN heterostructures by frequency-dependent admittance analysis, *J. Electron. Mater.* 39 (2010) 2681–2686.